TEXAS INSTRUMENTS

# **MICROSYSTEMS**

**Designers Handbook**

MICROPROCESSOR SERIESTM

2nd EDITION

# **CONTENTS**

# Section 1 The Texas Instruments Microsystem Range: An Introduction

# **Section 2** Single-chip microcomputers

|                                                   | Page   |

|---------------------------------------------------|--------|

| TMS 1000 Family – Introduction                    | 2-1    |

| Quick Reference Guide                             | 2-2    |

| TMS 1000/1200 – 4 bit PMOS Microcomputer          | 2-3    |

| TMS 1100/1300 – 4 bit PMOS Microcomputer          | 2-4    |

| TMS 1400/1600/1470/1670 – 4 bit Microcomputer     | 2-5    |

| TMS 1700 – 4 bit PMOS Microcomputer               | 2-6    |

| TMS 2100/2300/2170/2370 – 4 bit PMOS              |        |

| Microcomputer                                     | 2-7    |

| TMS 1000C/1200C/1100C/1300C – 4 bit CMOS          |        |

| Microcomputer                                     | 2-8    |

| TMS 1024/5 – TMS 1000 Family Input/Output expande | rs 2-9 |

| SE1 to SE5 – System Emulator Chips                | 2-10   |

| TMS 1601 NLL – PMOS controller/timer              | 2-11   |

| TMS 1121/1122 – Universal timer/controller        | 2-11   |

| TMS 1019 – Microprocessor based lighting system   | 2-12   |

| SEB 1, 2 and 3 – System emulation boards          | 2-13   |

| TP0401 – Liquid crystal display driver            | 2-14   |

| Application techniques                            | 2-15   |

| Applications                                      | 2-16   |

| Masking/Development Timescales                    | 2-17   |

| Packages/Reliability                              | 2-18   |

| TMS 7000 Family Introduction                      | 2-19   |

|                                                   | -20/21 |

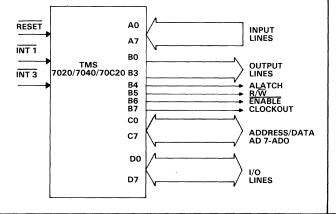

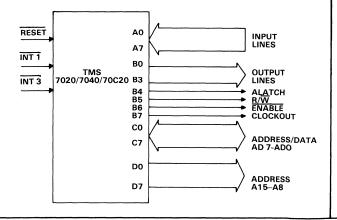

| TMS 7020/7040/70C20 – Expansion modes             | 2-22   |

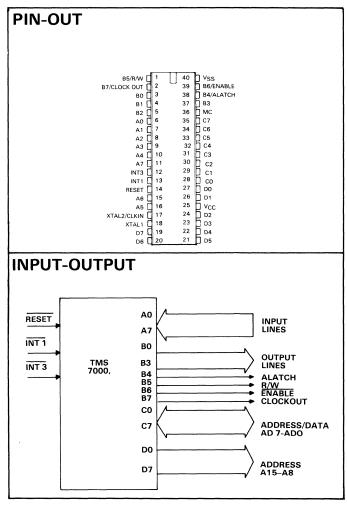

| TMS 7000 – 8 bit NMOS microprocessor              | 2-23   |

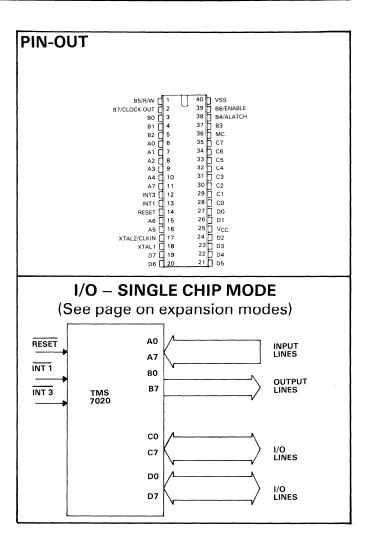

| TMS 7020 – 8 bit NMOS microcomputer               | 2-24   |

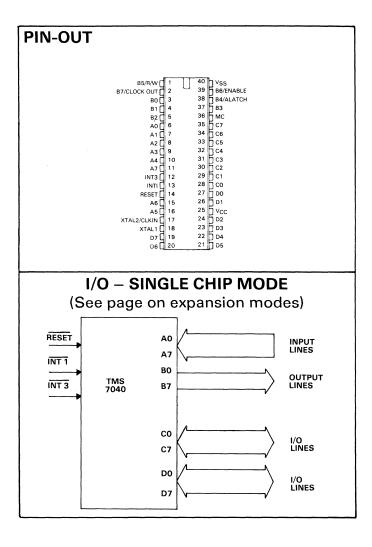

| TMS 7040 – 8 bit NMOS microcomputer               | 2–25   |

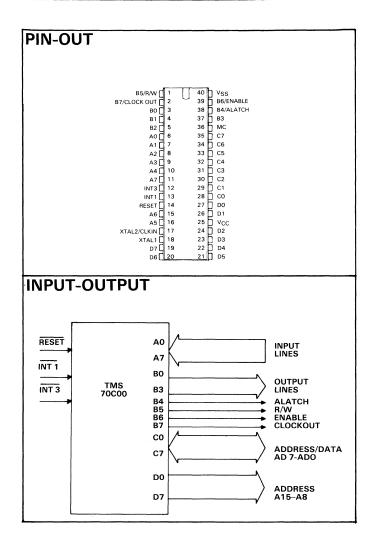

| TMS 70C00 – 8 bit CMOS microcomputer              | 2–26   |

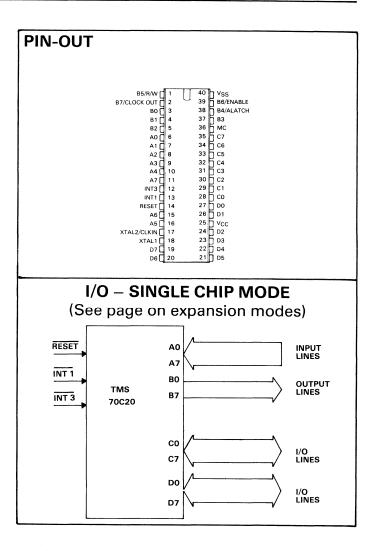

| TMS 70C20 – 8 bit CMOS microcomputer              | 2–27   |

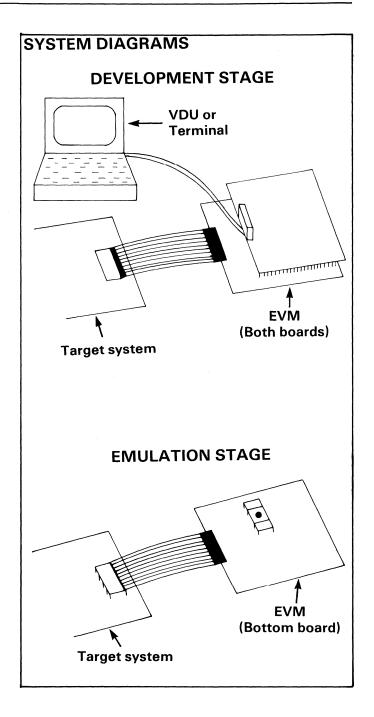

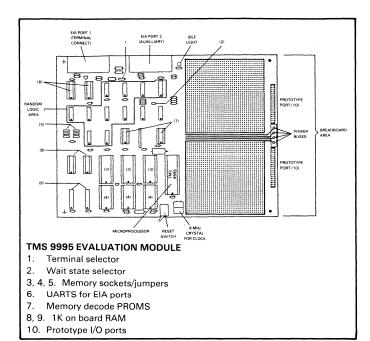

| TMS 7000 – Evaluation module                      | 2–28   |

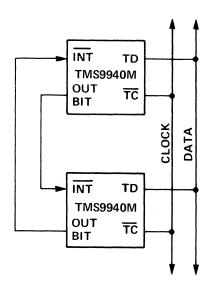

| TMS 9940 – Introduction                           | 2–29   |

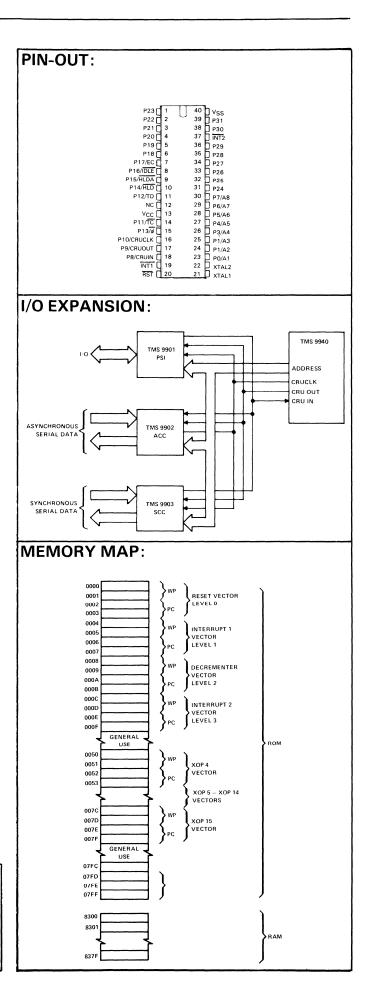

| TMS 9940 MCR – 16 bit NMOS microcomputer          | 2–30   |

| TMS 9940E – 16 bit NMOS microcomputer             | 2-31   |

## Section 3 Microprocessors

|                                                    | Page   |

|----------------------------------------------------|--------|

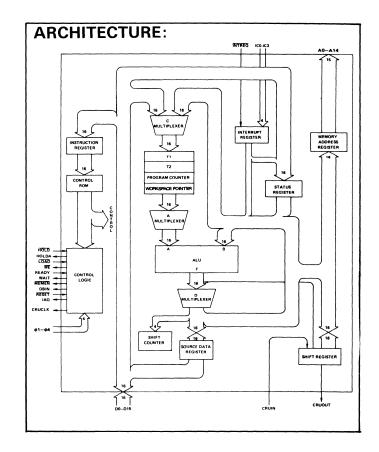

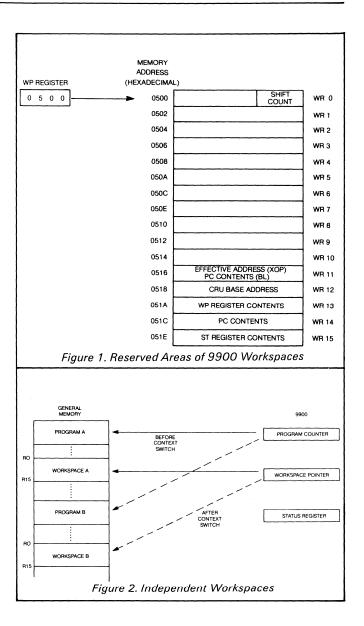

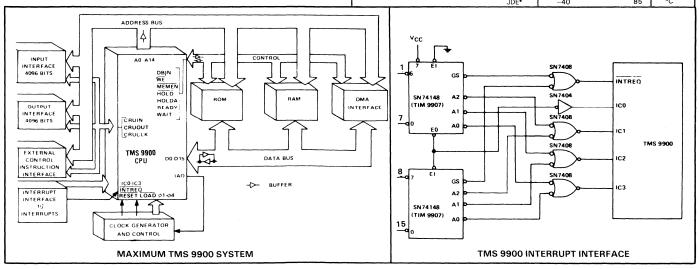

| TMS 9900 – Architecture                            | 3–1    |

| Memory-to-Memory – Architecture                    | 3–2    |

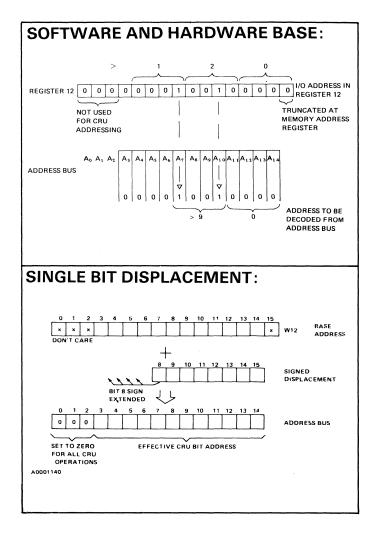

| Communications Register Unit (CRU)                 | 3–3    |

| TMS 9900 – Instruction speed                       | 3-4    |

| TMS 9900 – 16 bit microprocessor                   | 3-5    |

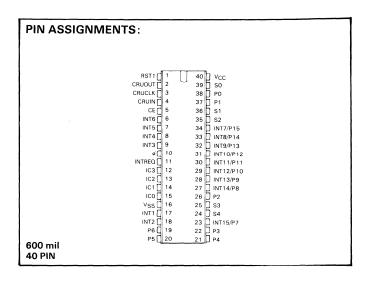

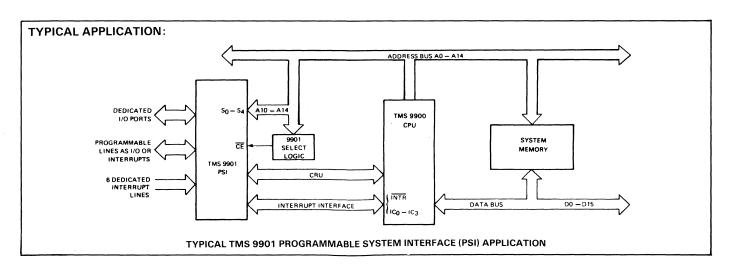

| TMS 9901 – Programmable systems interface          | 3–6    |

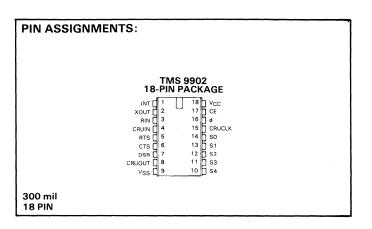

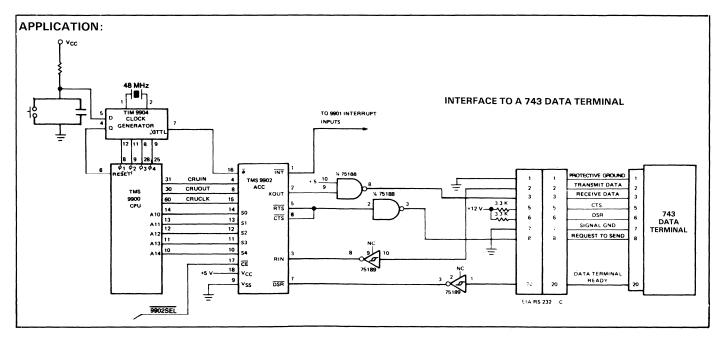

| TMS 9902 – Asynchronous communications controller  | 3-7    |

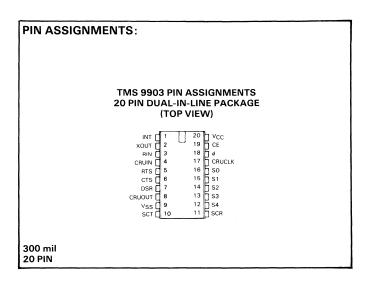

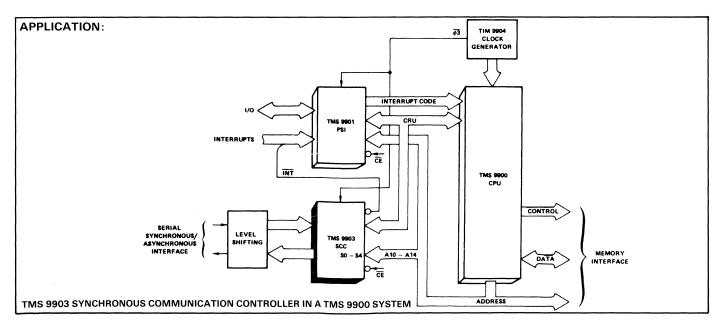

| TMS 9903 – Synchronous communications controller   | 3–8    |

| TMS 9902, 9903 – Line interfaces – selection guide | 3-9/10 |

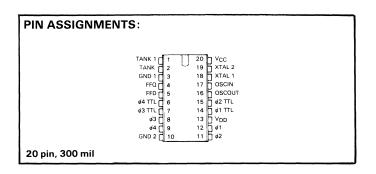

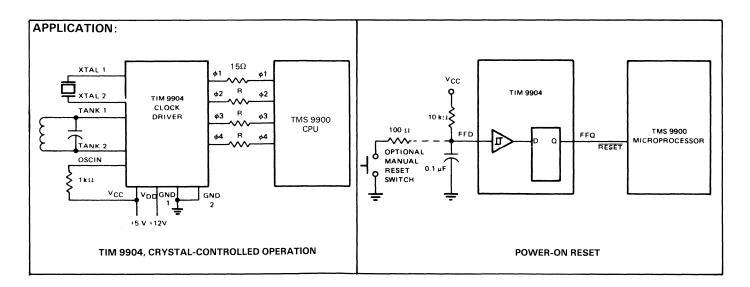

| TIM 9904 – Clock generator/driver                  | 3–11   |

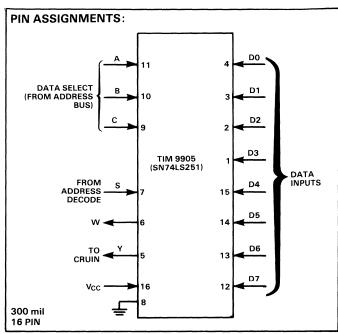

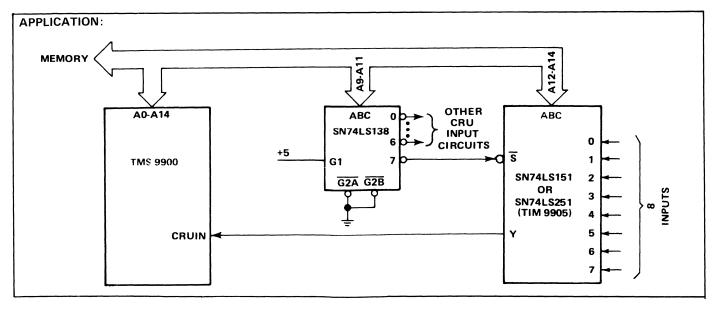

| TIM 9905 – Data selector/multiplexor               | 3–12   |

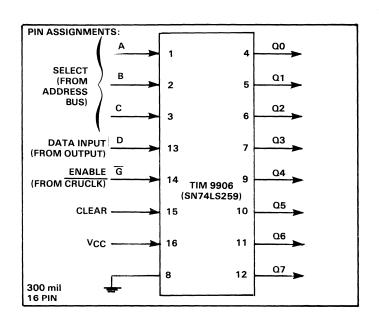

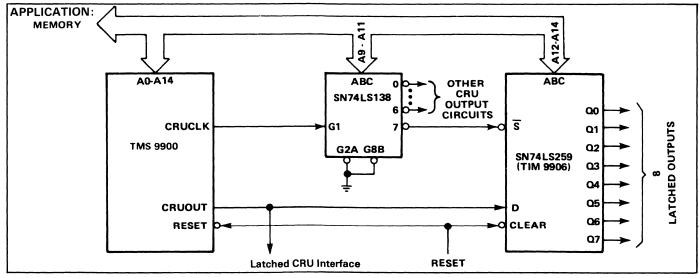

| TIM 9906 – 8 bit addressable latch                 | 3-13   |

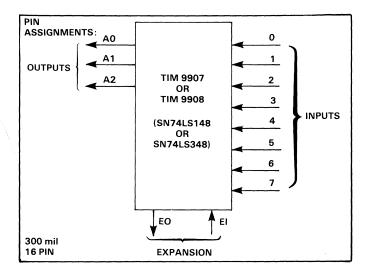

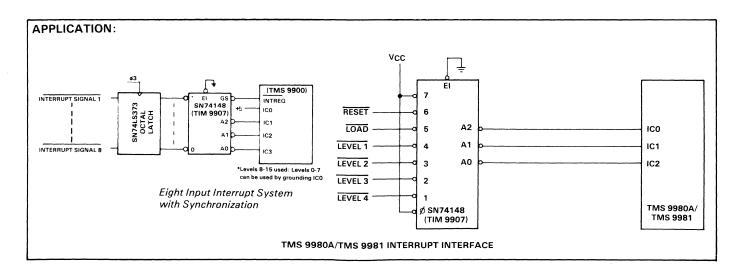

| TIM 9907/08 – 8 to 3 line priority encoders        | 3-14   |

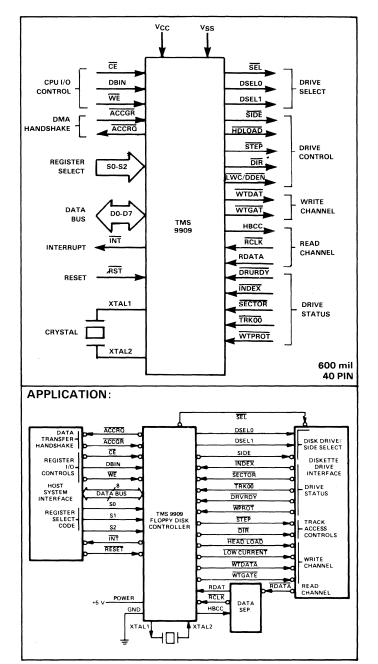

| TMS 9909 – Floppy disk controller                  | 3-15   |

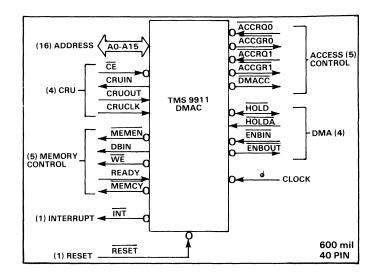

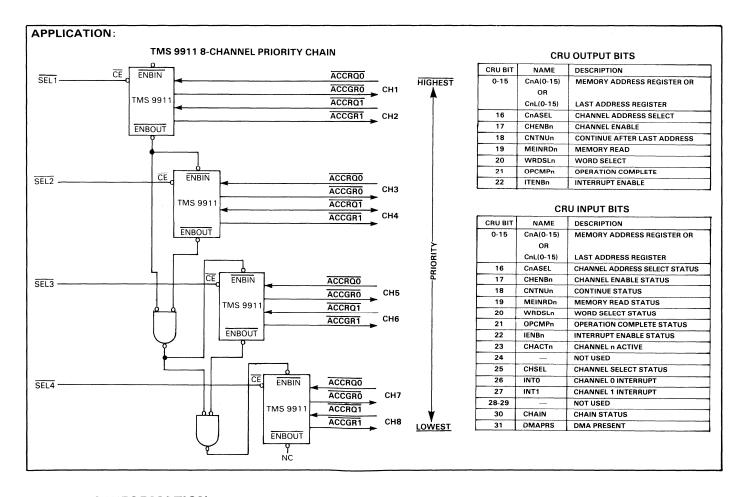

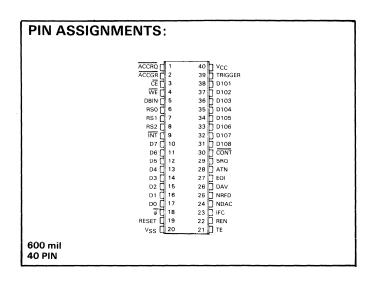

| TMS 9911 – DMA controller                        |          | 3 - 16 |

|--------------------------------------------------|----------|--------|

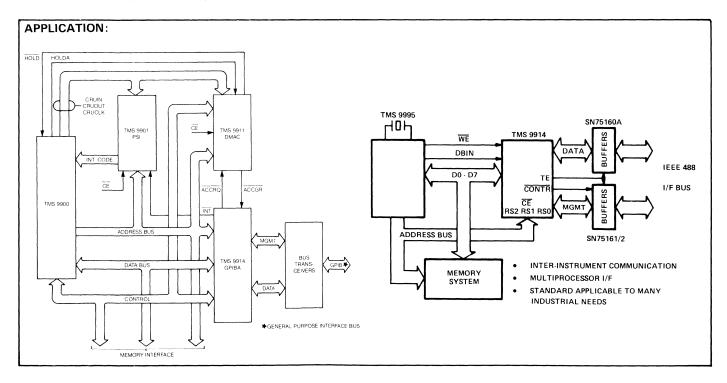

| TMS 9914A – GPIB Adaptor                         |          | 3-17   |

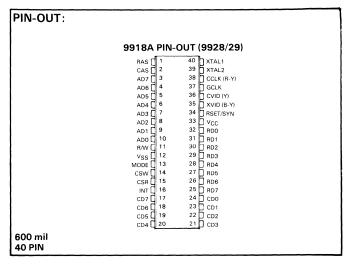

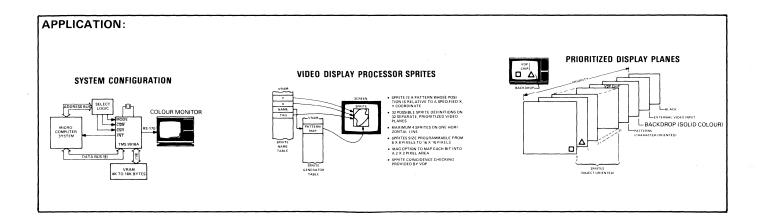

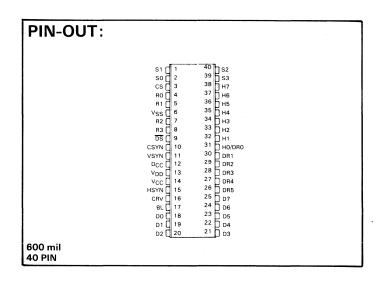

| TMS 9918A/28A/29A - Video display processor      |          | 3-18   |

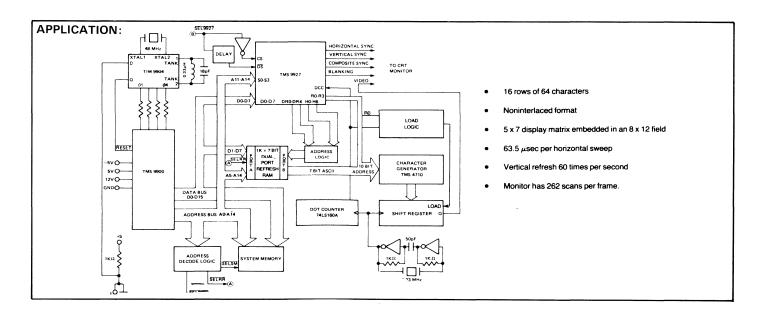

| TMS 9927/37 – Video timer/controller             |          | 3-19   |

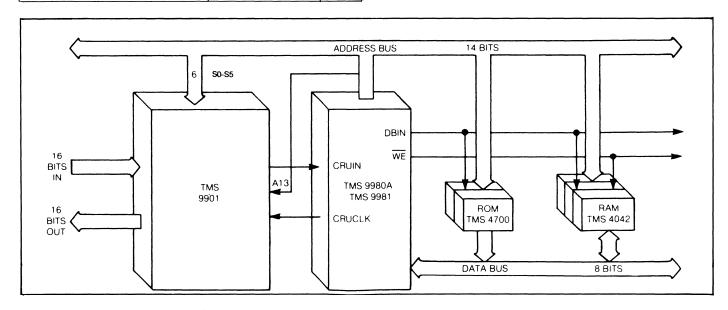

| TMS 9980A/81 - 16 bit microprocessor (8 bit da   | ıta bus) | 3-20   |

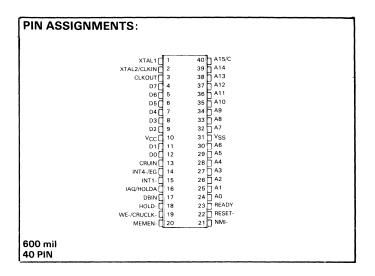

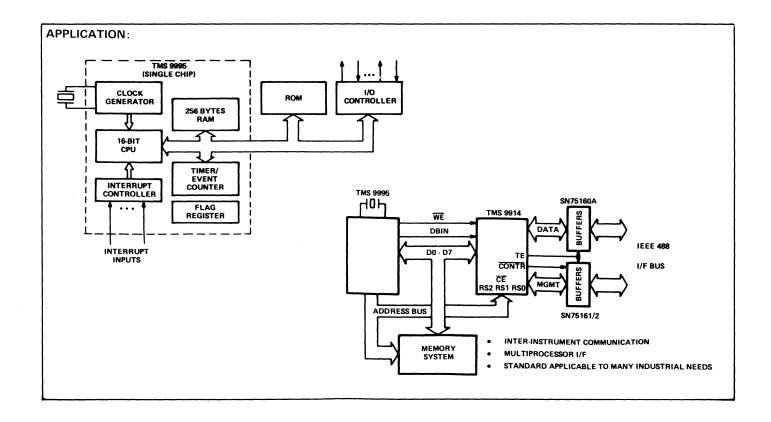

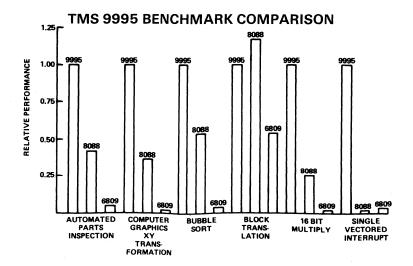

| TMS 9995 – 16 bit microcomputer                  | 3–2      | 21/22  |

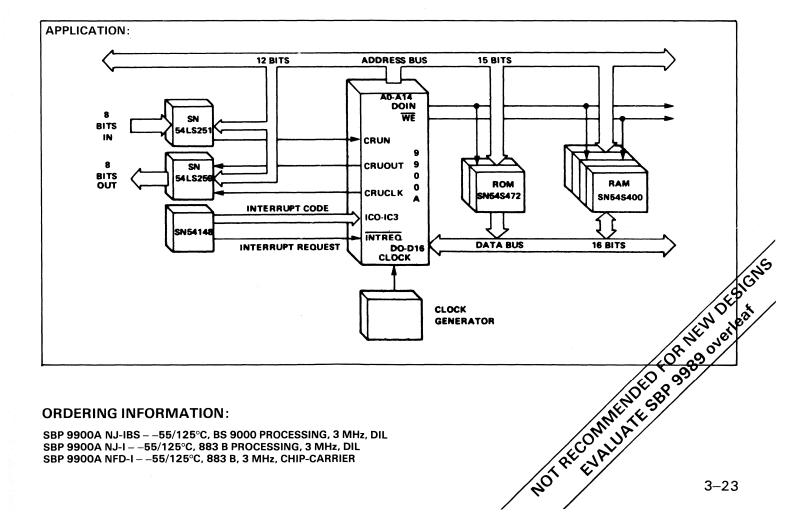

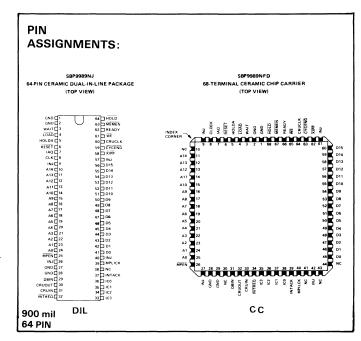

| SBP 9900A – 16 bit microprocessor                |          | 3–23   |

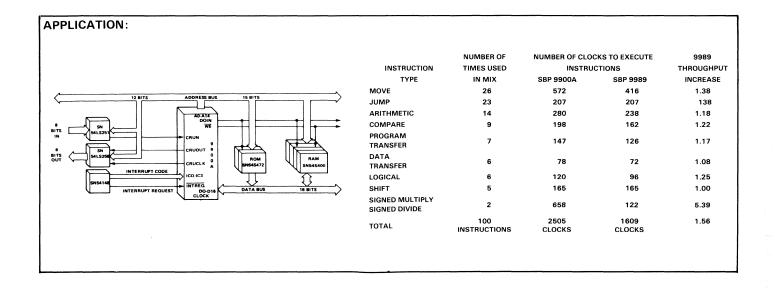

| SBP 9989 - Advanced 16 bit bipolar microproce    |          | 3–24   |

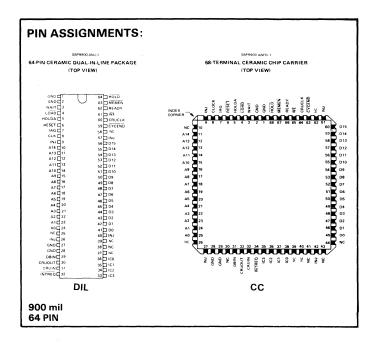

| TMS 99000 Series – Advanced 16 bit microproc     | essor    |        |

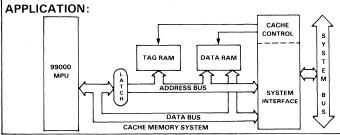

| family                                           |          | 3–25   |

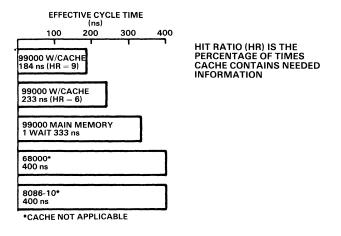

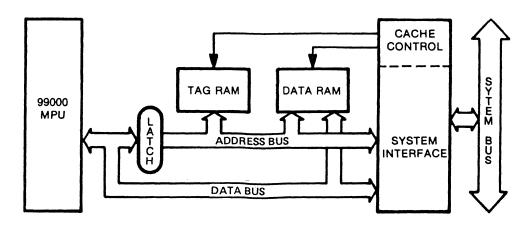

| TMS 99000 – System brief                         | 3-26 to  | 3–37   |

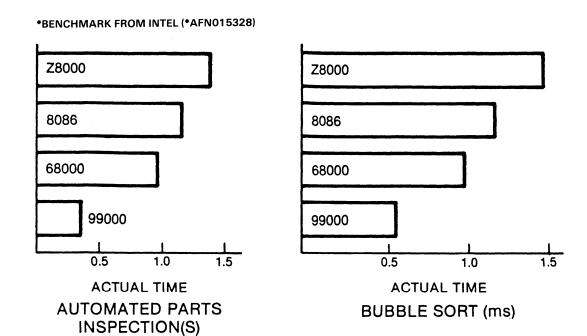

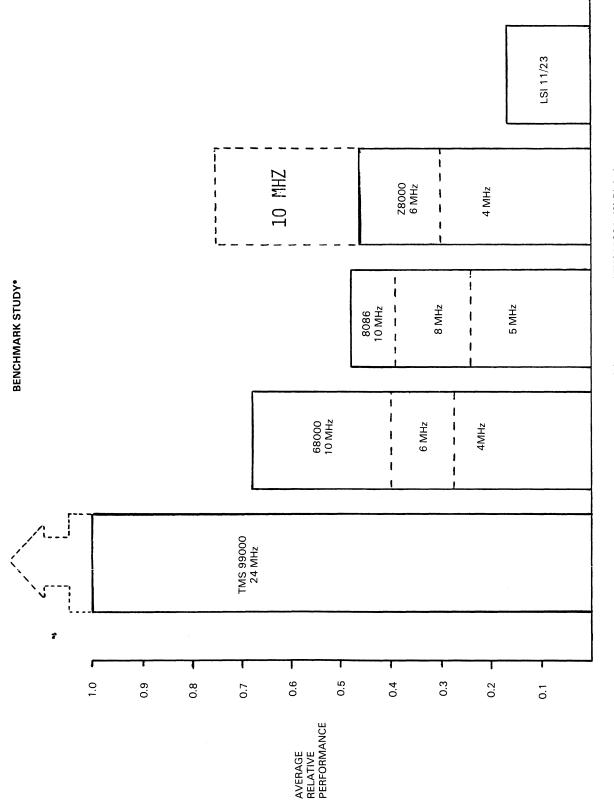

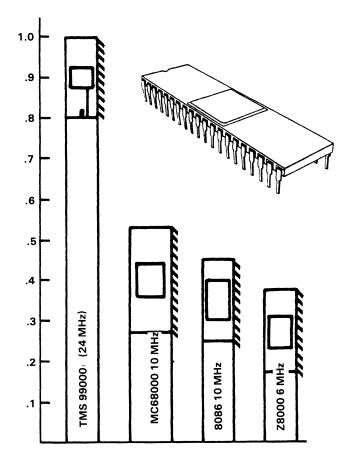

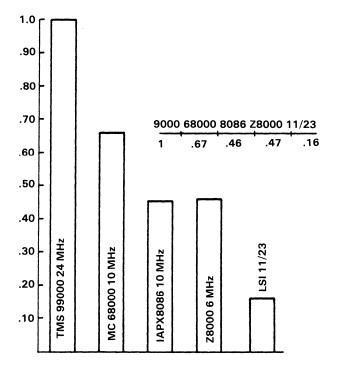

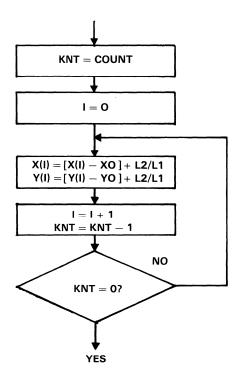

| TMS 99000 – Benchmark Report                     | 3–38 to  | 3–44   |

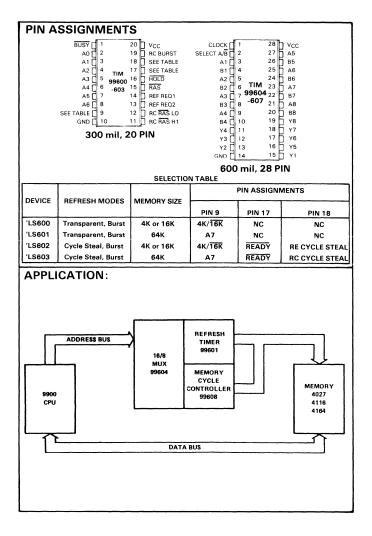

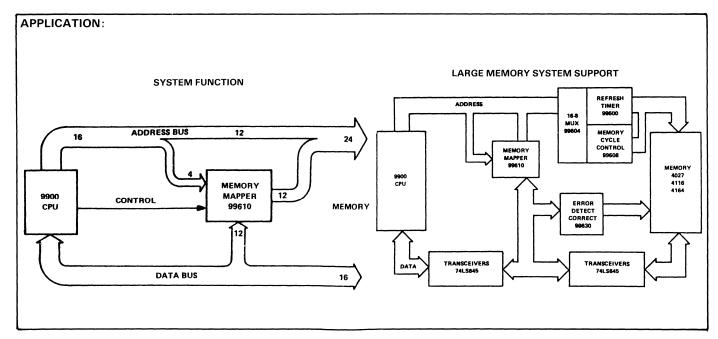

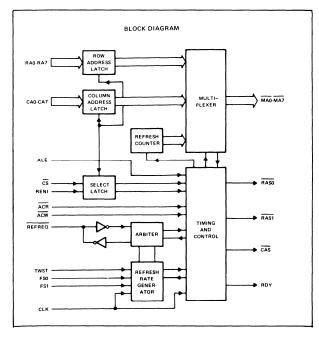

| TIM 99600/604/608 Series - Dynamic RAM refr      | esh      |        |

| controller circuits                              |          | 3–45   |

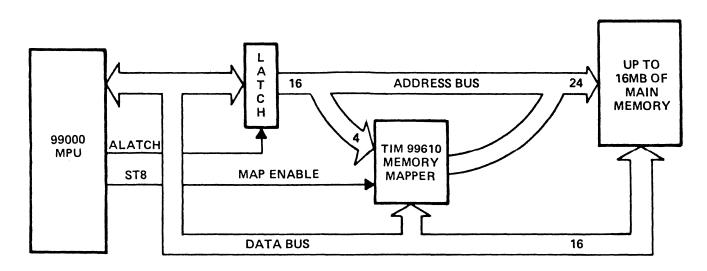

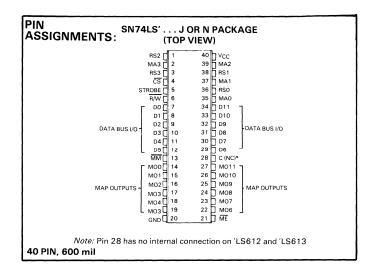

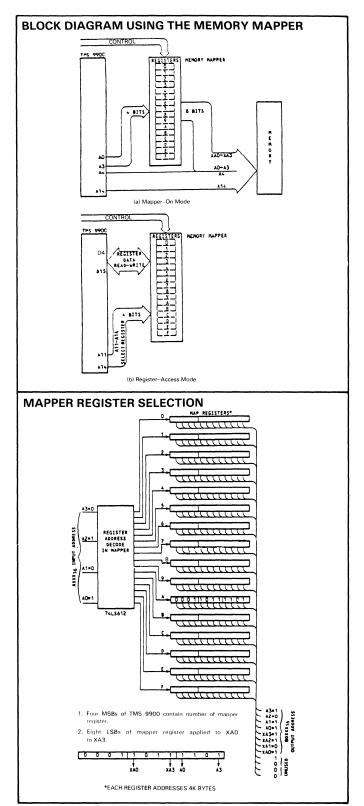

| TIM 99610/11/12/13 Series - Memory mapper        |          | 3–46   |

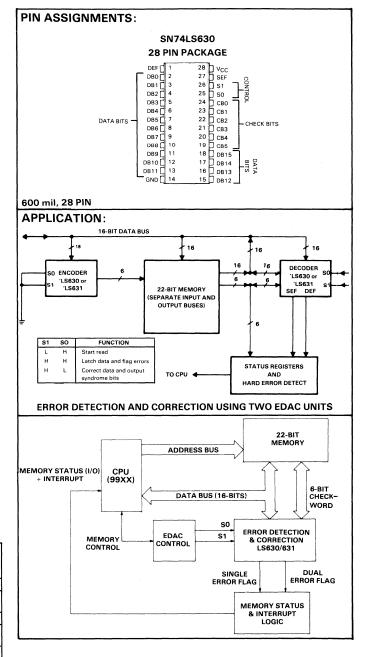

| TIM 99630/31 Series - Error detection and corre  | ction    |        |

| circuits                                         |          | 3–47   |

| TMS 4500NH – Dynamic Ram Controller              |          | 3–48   |

| BUS Interface - TTL Bus drivers/transceiver guid | е        | 3–49   |

| Memories                                         |          | 3–50   |

|                                                  |          |        |

# Section 4 Microcomputer boards

|                                                       | Page   |

|-------------------------------------------------------|--------|

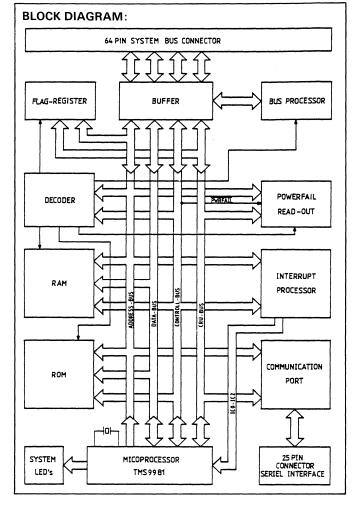

| TM990E/BUS – E-BUS microcomputer                      | 4-1    |

| TM990/E150A – E-BUS microcomputer                     | 4–2    |

| TM990/E151 - E-BUS system, standalone microcompute    | r 4–3  |

| TM990/E155 – E-BUS microcomputer                      | 4-4    |

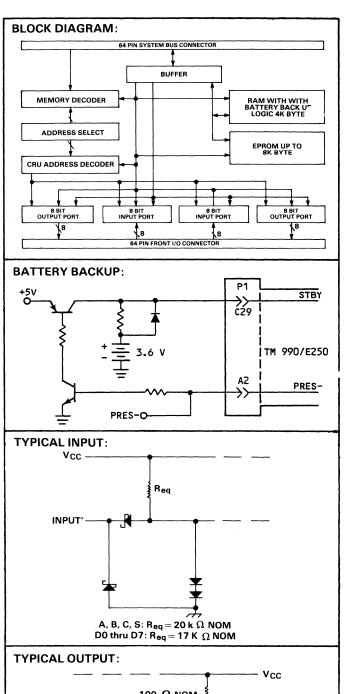

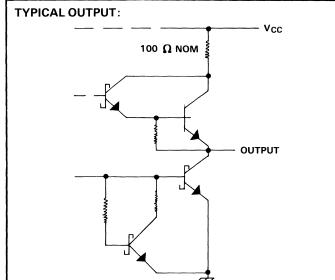

| TM990/E250 – E-BUS memory and I/O expansion           |        |

| module                                                | 4–5    |

| TM990/E251 – E-BUS RAM memory expansion module        | 4–6    |

| TM990/E255 – E-BUS memory expansion module            | 4–7    |

| TM990/E350 – E-BUS input expansion module             | 4–8    |

| TM990/E351 – E-BUS output expansion module            | 4–9    |

| TM990/E352 – E-BUS universal I/O module               | 4-10   |

| TM990/E353 - IEEE 488 (GPIB) Bus interface            | 4-11   |

| E-BUS Accessories                                     | 4-12   |

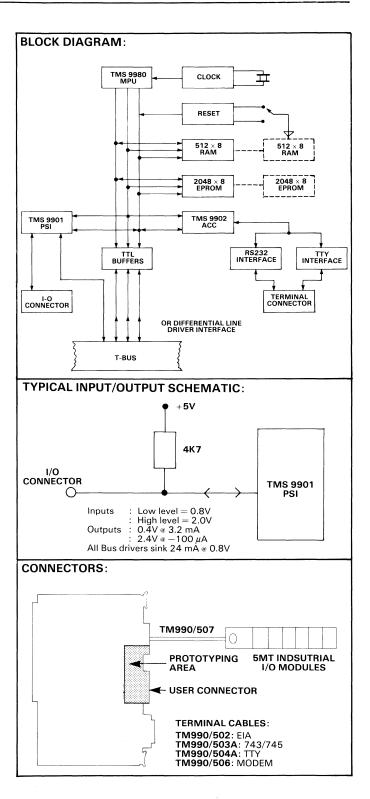

| TM990/BUS – T-BUS microcomputers                      | 4-13   |

| TM990/204 – T-BUS CMOS Ram module                     | 4-14   |

| TM990/602 – System hardware kit                       | 4-14   |

| TM990/601 – System hardware kit                       | 4–15   |

| TM990/600P – UCSD Pascal Development Software         | 4-15   |

| TM990/CXXX – Conformally coated boards                | 4-16   |

| TM990/100MA – T-BUS microcomputer                     | 4-17   |

| TM990/101MA – T-BUS microcomputer                     | 4-18   |

| TM990/102 – T-BUS extended memory CPU                 | 4-19   |

| TM990/180M – T-BUS microcomputer                      | 4-20   |

| TM990/189M – University board                         | 4 - 21 |

| TM990/1481 – T-BUS bit-slice processor board          | 4-22   |

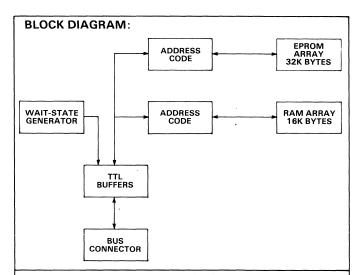

| TM990/201 – T-BUS memory expansion module             | 4-23   |

| TM990/203 – T-BUS memory expansion module             | 4-24   |

| TM990/206 – T-BUS memory expansion module             | 4-25   |

| TM990/301 – Microterminal                             | 4-26   |

| TM990/302 – Software development board                | 4-27   |

| TM990/303A – T-BUS floppy disc controller             | 4-28   |

| TM990/305 – Combination memory and input/output       |        |

| expansion module                                      | 4-29   |

| TM990/306 – Speech module                             | 4-30   |

| TM990/307 – T-BUS serial input/output expander card   | 4-31   |

| TM990/308 – T-BUS industrial communications module    | 4-32   |

| TM990/309 – T-BUS 6MT I/O Interface module            | 4-33   |

| TM990/310 - T-BUS parallel input/output expander card | 4-34   |

| TM990/311 – T-BUS parallel input/output expander card | 4-35   |

| TM990/314 – General purpose interface bus (GPIB)      |        |

| interface module                                      | 4-36   |

| TM990/317 – T-BUS counter timer module                | 4–37   |

| TM990/4XX – Software (TM990/400 Series)               | 4-38   |

| TMS QQO/5YY - Accessories                             | 4-39   |

# Section 5 Speech synthesis

|                                                  | Page |

|--------------------------------------------------|------|

| Solid State Speech – Introduction                | 5-1  |

| Words (1) – Custom speech data                   | 5–2  |

| Words (2) – "Off the shelf" speech library       | 5–3  |

| TMS 5100 – Voice synthesis processor             | 5-4  |

| TMS 5200 – Voice synthesis processor             | 5-5  |

| TMS 6100 – Voice synthesis memory                | 5–6  |

| TMS 6125 – Voice synthesis memory                | 5-7  |

| TMS 5220A – Voice synthesis processor            | 5–8  |

| Tinytalker – Speech evaluation board             | 5–9  |

| Superspeaker – Programmable Voice Computer       | 5-10 |

| PHROM EMULATOR – Voice synthesis memory emulator | 5-11 |

| Speech Development Laboratory                    | 5-12 |

| Applications                                     | 5_13 |

# Section 6 Development Systems and Software

|                                                     | Page |

|-----------------------------------------------------|------|

| AMPL – Advanced microprocessor prototyping          | Ü    |

| laboratory                                          | 6–1  |

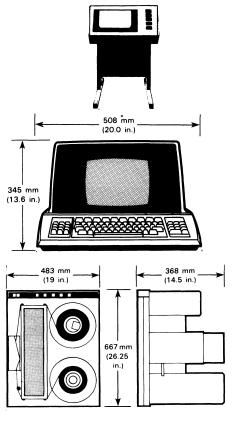

| TMAM 9001 – Single user development system          | 6–2  |

| TMAM 9010 – Multi-user hard disc AMPL system        | 6–3  |

| TMAM 9020 – Multi-user hard disc AMPL system        | 6–4  |

| TMAM 9040 – Multi-user hard disc AMPL system        | 6–5  |

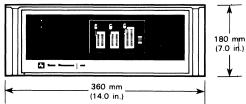

| TMAM 6001/2/3/4 – TMS 9900 Series AMPL stations     | 6–6  |

| TMAM 6093, 95 – TMS 9995 development                | 6–7  |

| TMAM 700X – Development system expansion parts      | 6–8  |

| Microprocessor Pascal                               | 6–9  |

| Component Software – EIA, HDLC, RX and Maths Pack   | 6–10 |

| Component Software - File Manager, Demice Independe | nt   |

| I/O and Data Pack                                   | 6-11 |

| Maintenance TM990/AMPL Repair procedures –          |      |

| UK Mainland                                         | 6–12 |

| Training Courses – Microprocessor training centre   | 6–13 |

| AMPL – 1000 system                                  | 6-14 |

| AMPL – 7000 system                                  | 6–15 |

47-1

# Section 1 The Texas Instruments Microsystem Range: An Introduction

# TEXAS INSTRUMENTS offers you the complete MICROSYSTEMS CAPABILITY SPECTRUM

It is safe to say choosing the required tools for designing microsystems can form a major and very important part of the development cycle.

Time spent here can favourably influence the overall development period and to an extent the outcome of the project. Whether it be a one-off or volume-produced system, or whether it is regarded as a complex or relatively simple application task, the process of selecting the basic elements encompasses many non-technical and technical aspects.

This Microsystems Designers Handbook with its product per page approach provides the means for making an optimum first glance technical assessment of the suitability of the micro-related products available from Texas Instruments. If your interest is triggered then more detailed data is available to back up the relevant products you require to investigate.

The overall demands made of a system give a rough and ready, unwritten, designer's guide to the processing power needed by the central processor unit (CPU) to meet a given task. Such a guideline involves the number of bits the CPU needs to handle in parallel or at any one instant in time (i.e. simultaneously).

In initial project discussions you will hear remarks such as "yes, that really needs a 16-bit microprocessor" or "with the addition of these latest features it's too much for a 4-bit machine". For example high volume consumer applications, such as a washing machine say, attract 4-bit and 8-bit single chip microcomputers. Medium volume Point-of-Sale Terminals tend to need 8-bit microprocessors (i.e. multi-chip solution) whilst in medium to low volume areas such as numerical tool control a 16-bit microprocessor is the best choice.

Texas Instruments offer a very diverse and unmatched range of microprocessor components to meet the complexity spectrum of applications which are being tackled today.

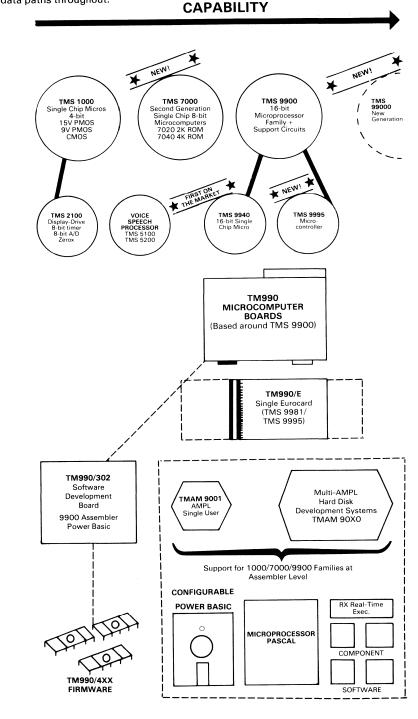

In brief terms there are three main microprocessor component families:

### 1. TMS 9900 Microprocessor Family

A range of 16-bit microprocessors and single-chip microcomputers backed by a comprehensive set of support circuits.

The TMS 9900, introduced back in mid-1976, was the first 16-bit microprocessor to be produced by a major semiconductor manufacturer.

One of the key strengths of the 9900 family is the strict software compatibility (at instruction-set level) that exists between the members. This makes it a comforting choice for the user who may find for example the TMS 9900 is a gross overkill for the application task and can within certain constraints transport the software onto say the lower cost, slower-throughput, TMS 9980A/81. In the family is the SBP 9900A which is a direct functional copy of the TMS 9900 but in the more robust I²L (Integrated Injection Logic) technology which enables it to meet military specifications.

The 9900 family also boasts the first 16-bit single chip microcomputer, TMS 9940M (masked part). For development only, there is the TMS 9940E (EPROM version).

To date there are numerous applications which have made use of the distinctive 9900 architectural features of context switching (ability to handle interrupts very fast) and the CRU I/O scheme (allows flexible bit manipulation very much akin to real world applications). The solutions adopted have withstood the microprocessor technology advances by competition.

With the TMS 9995 a number of common system functions have been integrated with the central processor function enabling 16-bit dedicated controller applications to be met by minimum package count but still retaining flexibility.

Where is the 9900 family philosophy heading?

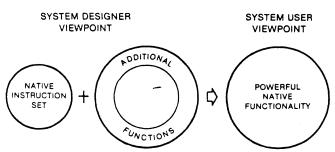

Well its the 99000 family a well thought out multi-processing network of highly intelligent functions. These functions are themselves based on fast 16-bit microprocessors similar in architecture to the 9900 family.

### 2. TMS 7000 Single Chip Microcomputer Family

This is Texas Instruments newly-launched family of second generation 8-bit chip microcomputers. The instruction set features multiply, flexible I/O manipulation, BCD arithmetic, powerful register-to-register operations (total of 128 general purpose memory-mapped registers) and versatile memory addressing modes.

The 7000 offers the user the unique ability to reconfigure the instruction set by microprogramming the Micro-Code ROM thereby adapting a particular microcomputer for a given application task.

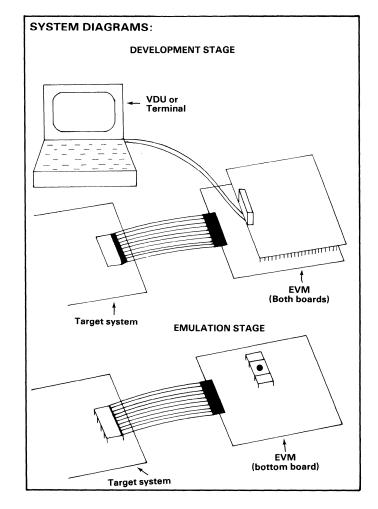

Experience of the family can be gained by using the TMS 7000 Evaluation Module which can also double up as an in-circuit emulator.

### *≺INTRODUCTION*

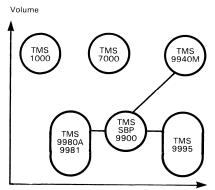

Relative Performance

The Performance/Volume Relationship of the Texas Instruments Microprocessor Families.

≺TMS 9900 MICROPROCESSOR FAMILY

THE FUTURE OF THE 9900 FAMILY TMS 99000!

≺TMS 7000 MICROCOMPUTER FAMILY As with the next family the single chip microcomputers offered are for volume applications where the on-chip ROM is mask programmed. There are three base members of this new NMOS family TMS 7020 (2K bytes ROM), TMS 7040 (4K bytes ROM) and TMS 7000 itself (ROMless). The family has been designed, right down to the chip layout itself, to comprehend the future enhancements being planned. These include producing the 7000 family in an alternative technology such as CMOS.

TMS 1000 > SINGLE CHIP MICROCOMPUTERS

3. TMS 1000 Single Chip Microcomputer Family

Well established family of 4-bit microcontrollers offered with various capacities of ROM, RAM and I/O, and, in various semiconductor technologies such as PMOS, 9V PMOS and CMOS.

Major architectural enhancements have resulted in the TMS 2100 series. These include direct display drive, a/d converter, timer/event counter and zero crossing detector.

It is ill-advised for the designer to adopt the traditional 4/8/16-bit demarcation attitudes towards these Texas Instruments microprocessor families.

This is never better typified than by the TMS 9980A/81 microprocessor and the more recent TMS 9995, microcontroller which have 16-bit capability on-chip, but an 8-bit external data bus. In fact, the TMS 9995 has a faster-throughput than its parent, TMS 9900, microprocessor with its 16-bit data paths throughout.

HOW TO APPROACH ➤

THE SELECTION

∠ 4-BIT? 8-BIT?

NRONG OR 16-BIT?

THE TEXAS

INSTRUMENTS

MICROSYSTEMS

SPECTRUM

**COMPONENTS**

Microprocessor Families

**Highlights**

MICROCOMPUTER MODULES

DEVELOPMENT SYSTEMS

**SOFTWARE**

Another example is the members of the TMS 7000 single chip microcomputer family which can be configured to be 8-bit microprocessors by setting an appropriate level on a particular pin (this is the TMS 7000 part itself).

With the TMS 7000 configured for peripheral expansion use can be made of some of the 9900 family support circuits. This is particularly true of the leadership. TMS 9914 GPIB IEEE-488 Adaptor (talker/listener/controller in one) and the unique TMS 9918A Video Display Processor (plus its derivatives TMS 9928, TMS 9929).

So the message is clear . . . particular attention needs to be paid in deriving the optimum solution from the products available.

Thought should also be given to the fact that the cost of the microprocessor is often a small part of the overall system cost and what was considered to be say a traditional 8-bit application would have best been tackled by 8/16-bitter such as the TMS 9980A/81 with the accompanying ease of use provided by the instruction set.

Before leaving components mention should be made of Texas Instruments' leadership voice speech processor chips. Recent breakthroughs in synthetic speech, based on a technique called linear predictive coding (LPC), have breached the long standing barriers to high-quality low-cost solid state speech. All that is needed is the speech processor chip, a vocabulary ROM and an optional local intelligent microcomputer controller (otherwise service from host or central processor).

Two speech synthesis circuits are available:

- 1. TMS 5100 mainly for high volume and optimised for use with single chip microcomputer.

- TMS 5200 low/medium volume; designed as a support circuit that can be easily driven by PIO or PIA part of a microprocessor based system.

Texas Instruments recognise that this existing technology is very much subjective and have made available a number of low-cost subsystems for evaluating speech (Tinytalker), for carrying out field trials and for cost effectiveness in low volume applications (Speech Library and EPSM).

Speech is radically changing the man/machine interface offering intelligent alarms, instructional commands, educational dialogues and such like in a diverse range of applications. Make sure you understand what it can do for you.

In addition to the 9900 family of components there is the TM990 range of microcomputer modules and firmware which are very attractive for applications where there is either

- insufficient time

- or low volume requirements

- r Imited hardware resources

- or a combination of these factors.

The TM990 range offers a do-it-yourself building block approach to solving your application. Based around the 16-bit 9900 microprocessor family the TM990 modules offer traditional minicomputer-type power for dedicated controller applications. These modules or supercomponents have been used in the actual end products manufactured (OEM typically 20 to 250 units); factory automation schemes as remote, intelligent, cost effective, stations, prototypes and test equipment to improve production.

There is the well established range of 'T' format size boards, TM990/XXX, which use the TMS 9900.

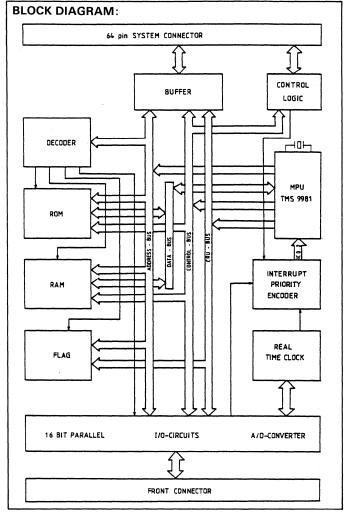

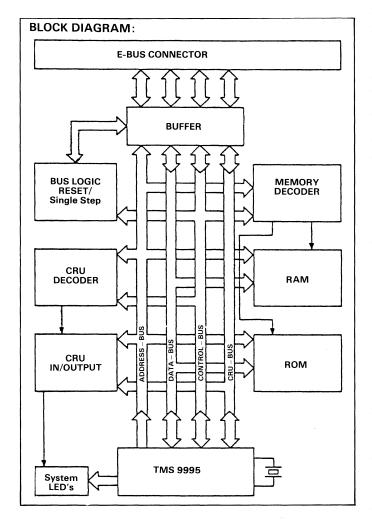

An alternative range of boards has recently been launched to complement the 'T' format. This is the TM990/EXXX range of single Euroboards (an internationally agreed standard) offering a highly modular/function approach to design. The boards are based on Texas Instruments' E-Bus which is a bus convention enabling multi-processing configurations. The Euroboards are centred around the TMS 9981 and the TMS 9995 processor. Both range of boards support distributed "ring main" style configurations running HDLC (High-Level Data Link Control) communication protocol. ('T' range: TM990/308 E-board range: TM990/E355)

Texas Instruments is fully committed to expand and fully support both board ranges.

If your application demands high speed precision computation there is the compatible TM990/1481 pair of boards emulating the 9900 architecture by the use of SN74S481 Schottky bit slices. The instruction set has been extended to support double precision (32-bit) and floating point arithmetic.

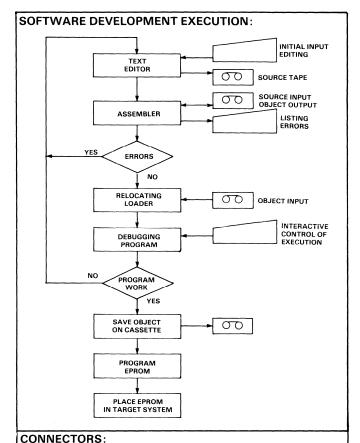

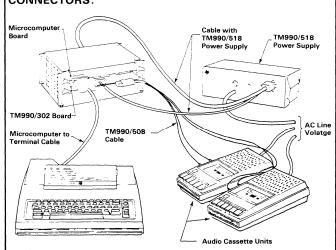

When it comes to writing software there is the low-cost development system available *within* the TM990 range which uses audio cassettes and allows programming of EPROM's. The TM990/302 Software Development Board, populated with the appropriate firmware, supports 9900 Assembler and Power BASIC programming.

Another interesting member which is useful for evaluating the 9900 architecture or for training the design team is the standalone educational TM990/189M University Board complete with full tutorial text and user's guide.

Let us now turn our discussion to Development Systems (the "workbench") and Software Support (the "tools") which are an important consideration in any project.

Important, because these represent a major investment in both money and people. Mistakes cannot be afforded.

Certain factors need to be assessed when looking at Development Systems:

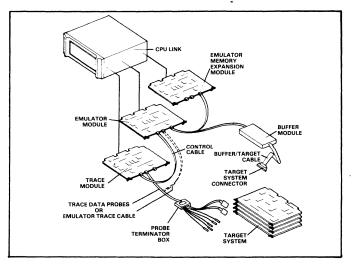

1. Assistance in System Integration (when the application software is being made to run on the target hardware) by provision of in-circuit emulation facilities.

EASE OF USE?

COMPATIBILITY?

DEV. TIME? CORRECT

S/W INVESTMENT?

**⋖SPEECH SYNTHESIS**

CAN YOUR DESIGN BENEFIT BY THE ADDITION OF SPEECH?

CAN SPEECH BE A USEFUL OPTION TO OFFER?

▼TM990

MICROCOMPUTER

MODULE RANGE

TWO RANGES

DISTRIBUTED COMPUTING HIGH SPEED APPLICATION?

LOW-COST SOFTWARE DEV. BOARD TM990/302

MICROPROCESSOR TEACH YOURSELF KIT

*<b>▼DEVELOPMENT SYSTEMS*

# WHAT TO LOOK FOR IN A DEVELOPMENT SYSTEM?

HIGH-LEVEL LANGUAGES

FOR TARGET SYSTEMS

- 2. Support for other microprocessors and microcomputers.

- 3. In addition to the expected assembler support the high-level language software support available.

- 4. The expandability of the system to cope with future requirements.

- Other uses of the system when not developing target system software e.g. automatic test equipment, logic state analyser, general purpose minicomputer, speech synthesis verification.

- 6. After Sales Support.

Texas Instruments offers software development support at assembler level plus full in-circuit emulation facilities for the TMS 9900, TM990, TMS 7000 and TMS 1000 product families on the following development systems:

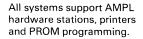

- TMAM 9001 single user floppy disk.

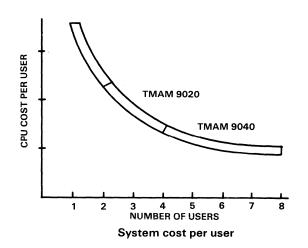

- TMAM 9010, 9020 and 9040 upgradable range of multi-user hard disk systems. They differ in size of memory, number of Video Display Terminals (users) and capacity of disk storage.

For 9900 target work and standalone logic state analyser operation there is the unique powerful interactive AMPL control language.

These are indeed universal development systems in a dedicated sort of way!

### **SOFTWARE** ►

As mentioned previously the diverse 9900 microprocessor family has a strict software compatibility at the instruction set level and this goes a long way to:

- Preserving software investment (software is said to form up to 75% of mpu projects today).

- Optimising people resources only need to train once.

This golden principle is further enhanced by the HLL's offered by Texas Instruments for the 9900/TM990 families. These are supplied in the form of easy-to-use self contained development packages. A unique feature is that account is taken of real world target system design constraints such as ROM/RAM partitioning, direct I/O manipulation, optimising interpreter overhead for a given application programme and allowing the designer to drop into assembler-type environment easily to handle say the time critical aspects of an application.

The Microprocessor HLL's available from TI are:

### Power BASIC (Interpretive)

Easy to learn and very popular language. Has a number of extensions which enable full manipulation of the hardware resources of a 9900-based system. Can handle interrupts within its high-level environment or transparently in assembler language.

It's supplied in the form of firmware for direct use on the TM990 range (Development Power BASIC) or on floppy disk for running on the Development Systems and optimising the final runtime interpreter support (Configurable Power BASIC).

# MICROPROCESSOR PASCAL

CONCURRENCY

**POWER BASIC**

IN-CIRCUIT EMULATION

DEBUGGING AT

STATEMENT LEVEL

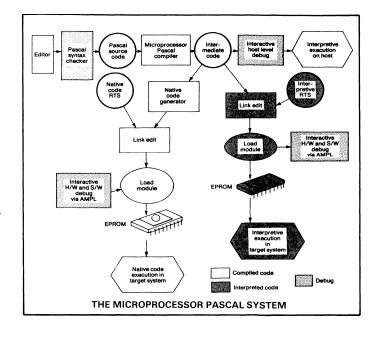

### Microprocessor PASCAL (MPP – Interpretive and Compilative Versions)

Pascal is gaining a great deal of popularity because it is a highly-disciplined structured language forcing the user to logically plan out the solution to his application. This in turn facilitates the future maintainability of the software.

MPP offers the customary features of the Pascal language but has a number of extensions which gives the designer that additional power to implement a solution quickly and reliably. One important extension is concurrency which allows the software to be written as a number of MPP processes (these are simply routines or collection of Pascal statements) each identifying with a particular hardware facility. MPP will run these processes concurrently and carry out the necessary organisation; there is no need to spend time writing an executive and inter-process communication procedures. If you remove a particular hardware facility you also remove the associated software process.

Another highly attractive feature is when you download your MPP programme using the in-circuit emulator onto the target system you can still debug and monitor at Pascal statement level. In other words you are able to debug the end application in the very same terms in which the application software was written. You do not have to resort to instructions and memory locations but stay with processes, statements, stack frames and so on.

Also key to the overall strategy is Texas Instruments' Component Software where standard software components are selected to facilitate and speed up the implementation of microsystems. Complete source listings are supplied so the user can configure his own component with only those features necessary for his application.

Similar to hardware components these software components plug into a bus which in this case is called RX – Real Time Executive. An example of a TI software component is the EIA Communications Package which supports file level communication over multi-port EIA links.

The spectrum of capability available from TI is indeed vast We trust this Microsystems Designers Handbook will serve as a quick, easy-to-use, very informative reference guide and will occupy a permanent ready-to-pick-up place on the design bench.

When you select a product then you can request more detailed data from the Customer Response Centre at our Bedford headquarters. Our resources do not stop there, you can discuss your requirements with our authorised distributors who operate TI Microsystem Design Centres. Additionally TI System Specialists are available to work in the field assisting in the design-in and development stages of the project.

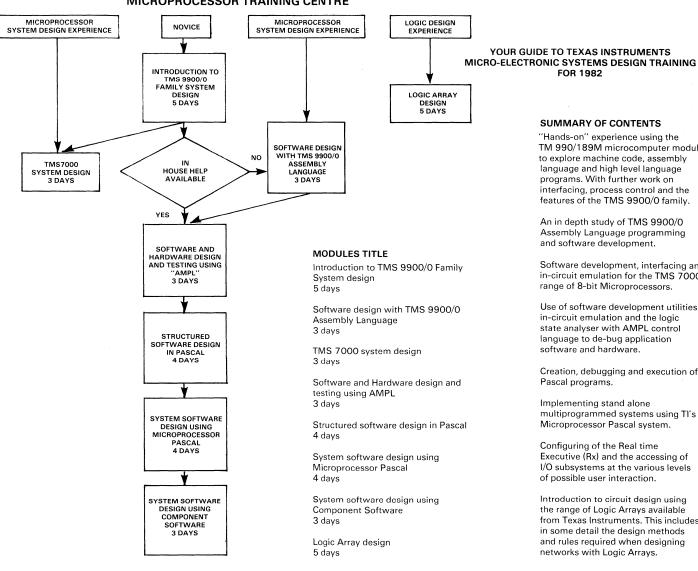

To speed up that all important getting-started phase TI has a Microprocessor Training School offering extensive in-depth training courses on all aspects of our products.

Happy Designing!

### **COMPONENT SOFTWARE**

SOFTWARE FUNCTIONS

DIRECTLY RELATED TO

HARDWARE FUNCTIONS

OUR SUPPORT ➤ SERVICES

TRAINING>

# Section 2 Single-chip microcomputers

# **AN INTRODUCTION TO THE TMS 1000**

4-bit MICROCOMPUTER FAMILY

### THE LOWEST COST SOLUTION

When your high volume (>5000 units) application involves a human-to-computer interface or a machine-to-computer interface, or a similar application with input/output speed restrictions, the TMS 1000 family will normally be the most cost-effective solution. A huge number of variants on the basic 4-bit architecture are available. Options include choice of memory size (0.5, 1, 2 or 4K ROM), variable amounts of I/O, vacuum fluorescent drive options, low power CMOS, A/D converters and many others. And a full complement of development aids are available.

Over 60 million TMS 1000 family units have been shipped worldwide, giving an unparalleled production experience and extremely high reliability.

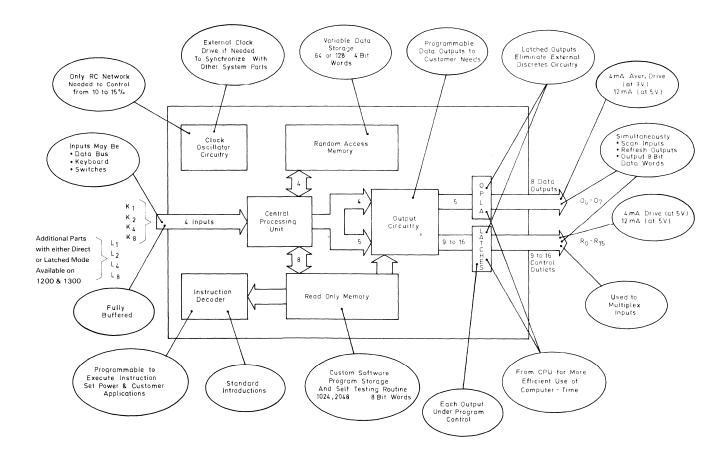

# ANATOMY OF A HIGH-VOLUME MICROCOMPUTER

The TMS 1000 series is a family of 4-bit microcomputers with a ROM, a RAM and an arithmetic logic unit on a single semiconductor chip. A customer's specification determines the software that is reproduced during wafer processing by a single-level mask technique that defines a fixed ROM pattern. The reference chart on the next page shows the various versions that are available so that a microcomputer can be chosen that best fits an application.

### **Block Diagram of CMOS Microcomputer**

# **Quick Reference Guide**

### TMS 1000 Family

| PART NUMBER                  |                            | 10XX  | 11XX  | 12XX  | 13XX  | 14XX | 16XX | 17XX |

|------------------------------|----------------------------|-------|-------|-------|-------|------|------|------|

| ROM $512 \times 8$ bits      |                            |       |       |       |       |      |      | Р    |

| $1024 \times 8$ bits         |                            | P,L,C |       | P,L,C |       |      |      |      |

| $2048 \times 8 \text{ bits}$ |                            |       | P,L,C |       | P,L,C |      |      |      |

| $4096 \times 8$ bits         |                            |       |       |       |       | P,L  | P,L  |      |

| RAM $64 \times 4$ bits       |                            | P,L,C |       | P,L,C |       |      |      |      |

| $128 \times bits$            |                            |       | P,L,C |       | P,L,C |      |      |      |

| OUTPUTS Port 1:              | 9 bit addressed            |       |       |       |       |      |      | Р    |

|                              | 10 bit addressed           | С     | С     |       |       |      |      |      |

|                              | 11 bit addressed           | P,L   | P,L   |       |       | P,L  |      |      |

|                              | 13 bit addressed           |       |       | P,L   |       |      |      |      |

|                              | 16 bit addressed           |       |       | С     | P,L,C |      | P,L  |      |

| Port 2:                      | 8 word addressed           | P,L,C | P,L,C | P,L,C | P,L,C | P,L  | P,L  | Р    |

|                              | 10 word addressed          |       |       | 1270P |       |      |      |      |

| INPUTS Port 3:               | 4 level sensitive          | P,L,C | P,L   | P,L   | P,L   | P,L  |      | Р    |

|                              | 4 level + 4 edge sensitive |       |       | С     | С     |      | P,L  |      |

| SUBROUTINES                  | 1 level, same page         | P,L   | P,L   | P,L   | P,L   |      |      | Р    |

|                              | 3 level any page           | С     | С     | С     | С     | P,L  | P,L  |      |

| OSCILLATOR                   | 300 kHz                    | P,L,C | P,L   | P,L,C | P,L   |      |      |      |

|                              | 600 kHz                    | P,L,C | P,L,C | P,L,C | P,L,C | P,L  | P,L  | Р    |

|                              | 1000 kHz                   | С     | С     | С     | С     |      |      |      |

| SUPPLY                       | 5V                         | С     | С     | С     | С     |      |      |      |

|                              | 9V                         | L     | L     | L     | L     | L    | L    |      |

|                              | 15V                        | Р     | Р     | Р     | Р     | Р    | Р    | Р    |

| I/O LEVELS                   | SUPPLY (XX00)              | P,L,C | P,L,C | P,L,C | P,L,C | P,L  | P,L  | Р    |

|                              | 30/35V (XX70)              | P,L,C | P,C   | P,L,C | P,C   | P,L  | P,L  | Р    |

| PACKAGE                      | 20 Pin                     |       |       |       |       |      |      | Р    |

|                              | 28 Pin                     | P,L,C | P,L,C |       |       | P,L  |      | Р    |

|                              | 40 Pin                     |       |       | P,L,C | P,L,C |      | P,L  | Р    |

\*P: PMOS

L: LOW VOLTAGE PMOS

C: CMOS

### TMS 2100 Family

| PART NUMBER            |          | 2100 | 2170     | 2300 | 2370     |

|------------------------|----------|------|----------|------|----------|

| Package: (28 pin       |          | V    | √        |      |          |

| ₹ 40 pin               |          |      |          | ✓    | ✓        |

| VF display interfacing |          |      | √        |      | √        |

| Analogue Input Lines   | <b>1</b> | √    | ✓        |      |          |

|                        | 2        |      |          | V    | V        |

| Independent Output     | 7        | √    |          |      |          |

| Lines                  | 6        |      | ✓        |      |          |

|                        | 15       |      |          | ✓    |          |

|                        | 14       |      |          |      | <b>√</b> |

| Digital Input Lines    | ∫ 8      | √    | <b>√</b> |      |          |

|                        | 12       |      |          | V    | V        |

|                        |          |      |          |      |          |

|                        |          |      |          |      |          |

|                        | 1        |      |          |      |          |

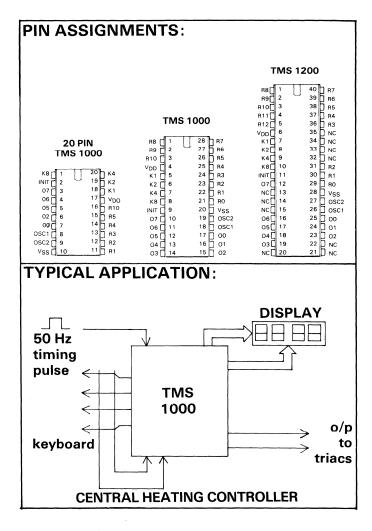

4-bit PMOS MICROCOMPUTER

### **FEATURES:**

- 1K of program memory.

- 64 nibbles of data memory.

- 20, 28 & 40 pin versions.

- Low-cost PMOS technology.

- 9V and 15V versions.

### **DESCRIPTION:**

TMS 1000 is the basic 1K ROM memory version of the TMS 1000 family suitable for a wide variety of microcontroller applications.

It is available in a 20-pin package for very cost sensitive applications with a reduced number of R & O lines.

It is very suitable for interfacing keyboards and displays for general purpose 'Human-Interface' applications.

HIGH VOLTAGE (Vacuum fluorescent drive) VERSION AVAILABLE

$\sqrt{}$

CMOS version available SE Emulator SE-1 TMS 1099 JLP

### **CHARACTERISTICS:**

| Supply voltage     | 9 or 15V |

|--------------------|----------|

| Supply current     |          |

| Av. R output drive |          |

| Av. O output drive | 24 mA    |

| Temp. range        | 0–70°C   |

### **ORDERING INFORMATION:**

MP XXXX-1000 TLP – 20 pin plastic MP XXXX-1000 NLP – 28 pin plastic MP XXXX-1200 NLP – 40 pin plastic

$\begin{array}{l} MP~XXXX-1070~NLP-28~pin~plastic\\ MP~XXXX-1270~NLP-40~pin~plastic \end{array}$

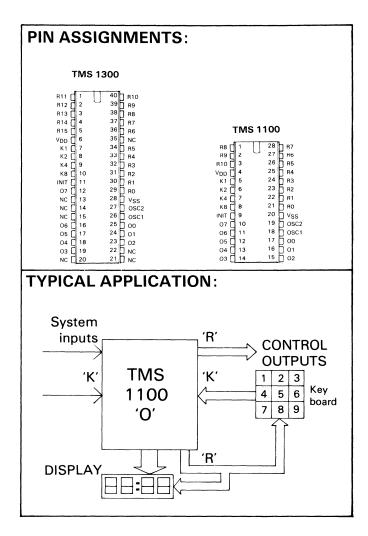

# TMS 1100/1300

### 4-bit PMOS MICROCOMPUTER

### **FEATURES:**

- 2K words of program ROM.

- 128 nibbles of data memory.

- 28 or 40 pin versions.

- 9V and 15V versions.

- Low-cost PMOS technology.

### **DESCRIPTION:**

For applications where the 1K program memory of the TMS 1000 is not sufficient, TMS 1100 may be used. It also offers twice the amount of RAM. Since it is a pin-for-pin compatible device, upgrading from TMS 1000 to TMS 1100 entails no PCB layout changes.

The TMS 1100 has a slightly modified instruction set to allow it to address twice the amount of ROM.

HIGH VOLTAGE (Vacuum fluorescent drive) VERSION AVAILABLE

$\sqrt{}$

CMOS version available SE Emulator SE-2 TMS 1098 JLP

# $\sqrt{}$

### CHARACTERISTICS:

| Supply voltage        | 9 or 15V |

|-----------------------|----------|

| Supply current (typ.) |          |

| Av. R output drive    | 14 mA    |

| Av. O output drive    | 24 mA    |

| Temp. range           | 0–70°C   |

### **ORDERING INFORMATION:**

MP XXXX-1100 NLP MP XXXX-1300 NLP

MP XXXX-1170 NLP MP XXXX-1370 NLP

High voltage output versions

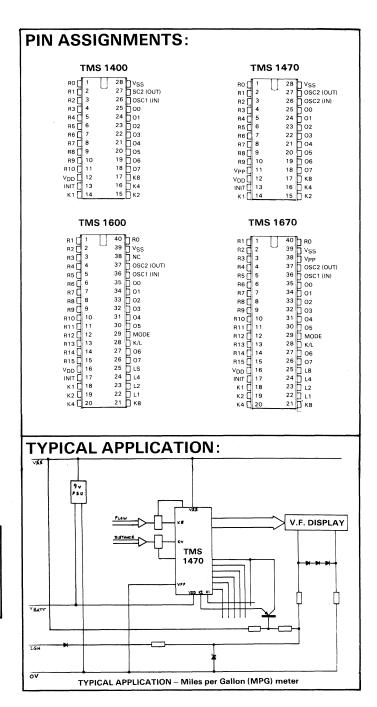

# TMS 1400/1600/1470/1670

4-bit PMOS MICROCOMPUTER

### **FEATURES:**

- 4K of program memory.

- 128 nibbles of data memory.

- 3 levels of subroutine.

- Mask programmable frequency divider on K8; four selectable options ÷ 1, 2, 10 or 20.

- 28 or 40 pin version.

- 4 latched and 4 unlatched inputs on 40 pin version.

### **DESCRIPTION:**

The TMS 1400/1600 offer the largest program memory size of the TMS 1000 family, for programs requiring more complex features or a larger number of features than can be handled by TMS 1100/1300. The on-board frequency divider reduces external hardware and simplifies many closed loop control systems. The devices are available in 9 or 15V PMOS only.

### **CHARACTERISTICS:**

| Supply voltage (av.)            |  |

|---------------------------------|--|

| Supply current (av.) typ 7 mA   |  |

| Max. R output drive (av.)       |  |

| Max. O output drive (av.) 24 mA |  |

| Temp. range0–70°C               |  |

HIGH VOLTAGE (Vacuum fluorescent drive) VERSION AVAILABLE

CMOS version available SE Emulator SE-5 TMS 1097 JLP

### ORDERING INFORMATION:

(600 mil plastic package)

MP XXXX-1400 NLL MP XXXX-1400 NLP

MP XXXX-1600 NLP

MP XXXX-1600 NLL

MP XXXX-1470 NLP MP XXXX-1470 NLP MP XXXX-1670 NLP MP XXXX-1470 NLL

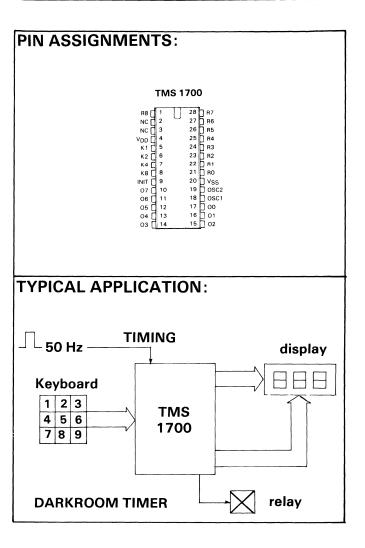

# **TMS 1700**

### 4-bit PMOS MICROCOMPUTER

### **FEATURES:**

- Minimum cost microcomputer.

- 0.5K program memory.

- 32 nibbles of data memory.

- Available in 20 or 28 pin DIL package.

### **DESCRIPTION:**

Lowest cost member of TMS 1000 family, the TMS 1700 is suitable for simple applications requiring a minimum of program memory. For example it could be programmed as a simple sound generator.

The TMS 1700 is available only in PMOS.

HIGH VOLTAGE (Vacuum fluorescent drive) VERSION AVAILABLE

CMOS version available SE Emulator SE-1 TMS 1099 JDL

### **CHARACTERISTICS:**

| Supply voltage (typ.) | 9 or 15V      |

|-----------------------|---------------|

| Supply current (typ.) | . 4 or 4.5 mA |

| Max. R output drive   | 28 mA         |

| Max. O output drive   | 14 mA         |

| Temp. range           | 0-70°C        |

### ORDERING INFORMATION:

MP XXXX-1700 NLP

These parts are available in 400 and 600 mil plastic packages and 300 mil 20 pin.

# TMS 2100/2300/2170/2370

### 4-bit PMOS MICROCOMPUTER

### **FEATURES:**

- On-chip A/D converter with 200μS sample time.

- 1 or 2 analog inputs.

- Event counter/interval timer.

- Zero crossing detector with noise debounce.

- Frequency divider on K8 input.

- Interrupt.

- 3 levels of subroutine.

### **DESCRIPTION:**

The top performance version of the TMS 1000 family, the TMS 2100 is well suited to all types of motor speed control or other applications involving phase control of triacs or similar.

The interrupt and timer facilities allow the 4-bit machine to perform a number of tasks normally associated with an 8-bit processor. TMS 2100 is only available in PMOS.

### **CHARACTERISTICS:**

| Supply voltage (typ.) | 9V     |

|-----------------------|--------|

| Supply current (typ.) |        |

| Max. R output drive   | 28 mA  |

| Max. O output drive   | 48 mA  |

| Temp. range           | 0-70°C |

HIGH VOLTAGE (Vacuum fluorescent drive) VERSION AVAILABLE

CMOS version available

### ORDERING INFORMATION:

MP XXXX-2100 NLP - 28 pin MP XXXX-2300 NLP - 40 pin

MP XXXX-2170 NLP – 28 pin MP XXXX-2370 NLP – 40 pin

These parts are available in 400 and 600 mil plastic packages and 600 mil ceramic.

### 4-bit CMOS MICROCOMPUTERS

### FEATURES: (in addition to PMOS)

- Low Power Consumption:

Normal operation ............ 3.5 mW

Standby mode (memory retained) ..5μW

- 3V operating Voltage minimum.

- 3 levels of subroutine.

- 28 and 40 pin DIL versions.

- 40 pin version has latched inputs.

- Clock frequency of up to 1MHz for faster operation.

### DESCRIPTION

These CMOS microcomputers offer the advantages of low voltage and low power. For example they may be used in battery powered products for long life, or directly powered from a telephone line. The ability to operate in the standby (or HALT) mode enables the contents of the RAM to be saved when the unit is not operating, only using  $5\mu$ W.

### **CHARACTERISTICS:**

| PIN ASSIGNMENTS:                          |                   |

|-------------------------------------------|-------------------|

|                                           | TMS 1200/1300C    |

| TMS 1000/1100C  K1                        | K1 [              |

| TYPICAL APPLICATION:                      |                   |

| MF<br>DIALLER                             | SPEECH<br>CIRCUIT |

| HOOK SWITCH SUITCH SO91                   | 1CM 1701          |

| TMS<br>1000 C<br>BUFFER                   | RINGER            |

| A 1 2 3<br>B 4 5 6<br>C 7 8 9<br>D * 0 ## |                   |

| PULSE DIAL TELEPHO<br>NUMBER STORAGE FA   |                   |

|                                              | TMS 1000 C TMS 1200 C |         | TMS 1100 C | MS 1100 C TMS 1300 C |               | TMS 1 × 70 C |               |  |

|----------------------------------------------|-----------------------|---------|------------|----------------------|---------------|--------------|---------------|--|

| Pkg. pin count                               | 28 pins               | 40 pins | 28 pins    | 40 pins              | 28 pins       |              | 40 pins       |  |

| Instruction ROM                              | 1024 >                | 8 bits  | 2048 >     | × 8 bits             | 1024 × 8 bits |              | 2048 × 8 bits |  |

| Data RAM                                     | 64 ×                  | 4 bits  | 128 ×      | 4 bits               | 64 × 4 bits   |              | 128 × 4 bits  |  |

| "R" individually addressed<br>output latches | 10                    | 16      | 10         | 16                   | 10            |              | 16            |  |

| Max. rated voltage<br>(O, R and K)           | 6 V                   |         | 6 V        |                      | −30 V to +7 V |              |               |  |

| Data inputs                                  | 4 8 4 8               |         | 4          | 8                    | 4             | 8            |               |  |

| Instruction set                              | 43                    |         | 43         |                      | 43            |              |               |  |

| Power supply                                 | 3-6 V                 |         | 3-6 V      |                      | 3–6 V         |              |               |  |

| Typ. dissipation                             | 3.5                   | mV      | 5 mW       |                      | 5 mW          |              |               |  |

| Clock frequency                              | 1 MHz max.            |         | 1 MHz max. |                      | 1 MHz max.    |              |               |  |

| Subroutine levels                            | 3                     |         | 3          |                      | 3             |              |               |  |

| Halt (power down)                            | Yes (                 | 5 μW)   | Yes (5 μW) |                      | Yes (5 μW)    |              |               |  |

| Temp. range                                  | 0-70°C                |         |            |                      |               |              |               |  |

HIGH VOLTAGE (Vacuum fluorescent drive) VERSION AVAILABLE

$\checkmark$

### **ORDERING INFORMATION:**

MP XXXX-1000 NLC MP XXXX-1200 NLC MP XXXX-1100 NLC M

MP XXXX-1300 NLC

MP XXXX-1070 NLC MP XXXX-1270 NLC MP XXXX-1170 NLC

MP XXXX-1370 NLC

Note:

SE Emulators: SE-3 TMS 1099 JLC SE-4 TMS 1098 JLC

SE-3 is used for emulation of TMS 1000C and TMS 1200C; SE-4 is used for

TMS 1100C and TMS 1300C.

These parts are available in 400 and 600 mil plastic packages and 600 mil ceramic.

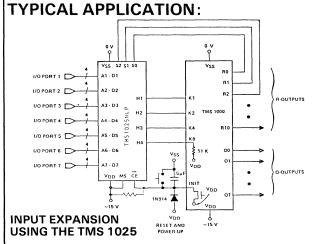

### TMS 1000 FAMILY INPUT/OUTPUT EXPANDERS

### **FEATURES:**

- Four or seven 4-bit I/O ports with latched output.

- Static operation.

- Compatible with TMS 1000 family.

- Chip enable to allow connection of several expanders in parallel.

- PMOS or CMOS technology.

- TTL compatible.

- Low power consumption.

### **DESCRIPTION:**

TMS 1024/5 are designed to extend the input/output capability of the TMS 1000 family. Depending on package size (28 or 40 pin) they give 4 to 16 line expansion or 4 to 28 I/O lines. The expansion lines may be configured as either input or output; and because of their static operation offer a 28-bit storage capability.

Both 9V and 15V versions are available in PMOS. there is also a 5V CMOS version.

### CHARACTERISTICS:

|                                      | Low Power<br>TMS 1024 NLL | Standard<br>TMS 1024 NLL | Low Power<br>TMS 1025 NLL | Standard<br>TMS 1025 NLP |  |

|--------------------------------------|---------------------------|--------------------------|---------------------------|--------------------------|--|

| Package Pin Count                    | 28                        | Pin                      | 40                        | Pin                      |  |

| Multiplexer Mode                     | 16-line                   | to 4-line                | 28-line                   | to 4-line                |  |

| Chip enable                          | Y                         | es                       | Yes                       |                          |  |

| Latch Mode                           | Four 4-bi                 | t Storage                | Seven 4-bit Storage       |                          |  |

| Clear Function                       | Y                         | es                       | Yes                       |                          |  |

| Power Supply/<br>Typical Dissipation | -9V/22.5mW                | -15V/60mW                | -9V/22.5mW                | -15V/60mW                |  |

| Operating Temp. range                | 0-70°C                    |                          |                           |                          |  |

HIGH VOLTAGE OUTPUT (Vacuum fluorescent drive) **VERSION AVAILABLE**

**CMOS VERSION AVAILABLE**

**ORDERING INFORMATION:** (600 mil plastic package)

TMS 1024 NLP: **Standard PMOS** TMS 1025 NLP: Standard PMOS TMS 1024 NLL: Low power PMOS TMS 1025 NLL: Low power PMOS

TMS 1025 NLC: TMS 1024 NLC: **CMOS CMOS**

**PIN ASSIGNMENTS: TMS 1025 NLP TMS 1025 NLL TMS 1024 NLP** MS C **TMS 1024 NLL** 29 28 27

### SYSTEM EMULATOR CHIPS

### **FEATURES:**

- True emulation of masked microcomputers.

- Extra status and control lines that are useful in debugging.

### **DESCRIPTION:**

These emulators are TMS 1000 family devices which are configured to work with an external program memory (usually in Eprom form) and an external Output Programmable Logic Array (usually a bipolar prom.).

These are the only differences between an SE device and the appropriate masked microcomputer.

High voltage devices are emulated by putting one transistor on each input or output line.

System Emulation devices have the following part numbers:

SE-1 = TMS 1099 JLP Note: All SE devices SE-2 = TMS 1098 JLP are available only in SE-3 = TMS 1099 JLC 64 pin ceramic packages. SE-4 = TMS 1098 JLC packages. SE-5 = TMS 1097 JLP

SE-6 = TMS 1096 JLP

Any TMS 1000 family microcomputer can be emulated by designing an SE device, Eprom and OPLA Prom into the prototype concerned. However, development is greatly simplified by using a System Emulation Board, which has these, and other components, on board, and then connecting the SEB to the prototype by a 28 or 40 pin connector.

For details on the range of SEB's available, see the Section on Emulator Boards.

| PIN ASSIGNI                        | <b>MENTS</b>                  |                                              |                       |

|------------------------------------|-------------------------------|----------------------------------------------|-----------------------|

|                                    | nd SE-2                       | SE-3                                         | and SE-4              |

| NC 1                               | 64 NC                         | V <sub>DD</sub> [ ]                          | 64 01                 |

| NC 2 2                             | 63 5 08<br>62 17              | osc2 2                                       | 63 601                |

| 04   3<br>NC   4                   | 61 16                         | osc3                                         | 62 5 02<br>61 04      |

|                                    | 60 15                         | INIT C 5                                     | 60 <del> </del> 08    |

| 02 [] 5<br>NC [] 6<br>01 [] 7      | 59 14<br>58 13                | CLR 6<br>L1 7                                | 59 5 OSL<br>58 5 ST   |

| 01 7<br>NC 8                       | 57 OSL                        | L2   8                                       | 57 X2                 |

| osc1 🛛 9                           | 57 OSL<br>56 12               | L4 🗍 9                                       | 56 X1                 |

| osc2 ☐ 10<br>Vss ☐ 11              | 55 NC<br>54 11                | L8 ☐ 10<br>K/L ☐ 11                          | 55 NC*<br>54 CA, SE-4 |

| RO 12                              | 53 NC                         | K1   12                                      | 53 H YA               |

| R1 13                              | 52 0                          | к2 🗍 13                                      | 52 YB                 |

| R2 [ 14<br>CA, SE-2 (NC,SE-1) [ 15 | 51 NC<br>50 PA0               | K4 ☐ 14<br>K8 ☐ 15                           | 51 R15<br>50 R14      |

| DCE [] 16                          | 49 NC                         | SE [ 16                                      | 49 🖥 R13              |

| PC4 17                             | 48 🗖 INIT                     | 10 🔲 17                                      | 48 E R12              |

| PC3 [ 18<br>PC2 [ 19               | 47 PA1<br>46 K8               | 11 [ 18<br>12 [ 19                           | 47 R11<br>46 R10      |

| PC1 20                             | 45 📙 K4                       | 13 20                                        | 45 R9                 |

| NC ☐ 21                            | 44 K2                         | 14 🔲 21                                      | 44 R8                 |

| R3 [ 22<br>R4 [ 23                 | 43   K1<br>42   PA3           | 15 🔲 22<br>16 🗍 23                           | 43 R7<br>42 R6        |

| R5 24                              | 41 PA2                        | 17 🗍 24                                      | 41 R5                 |

| NC 25                              | 40 V <sub>DD</sub>            | V <sub>SS</sub> C 25<br>PAO C 26<br>PA1 C 27 | 40 R4                 |

| NC 26<br>R6 27                     | 39 NC<br>38 R15*              | PAO   26                                     | 39 R3<br>38 R2        |

| R7 28                              | 37   R14*                     | PA2 28                                       | 07 lb                 |

| R8 ∐ 29                            |                               | PA3 ∐ 29                                     | 36 D PO               |

| R9 [] 30<br>R10 [] 31              | 24 15                         | PC0 0 30<br>PC1 31                           | 35 PC5<br>34 PC4      |

| PC0 [ 32                           | 33 R11                        | PC2 32                                       | 33 PC3                |

|                                    | SE-5 TMS 1                    |                                              |                       |

|                                    | VSS [ 1 PC5   2               | 64 X2<br>63 X1                               |                       |

|                                    | PCA HI a                      | 62 PA3                                       |                       |

|                                    |                               | 61 PA2                                       |                       |

| 1                                  | PC2 5<br>PC1 6                | 60 PA1<br>59 PA0                             |                       |

|                                    | PCO 7                         | 58 CA2                                       |                       |

|                                    | 10 🗍 8                        | 57 CA1                                       |                       |

|                                    | 11 [] 9<br>12 [] 10           | 56 OSC2<br>55 OSC1                           |                       |

|                                    | 12 🗖 44                       | 54 17 01                                     |                       |

| 1                                  | 14 12                         | 53 08                                        |                       |

|                                    | 14   12<br>15   13<br>16   14 | 52 04<br>51 02                               |                       |

|                                    | 17 🗍 15                       | 50 📙 01                                      |                       |

|                                    | RO ∐ 16                       | 49 OSL                                       |                       |

|                                    | R1 [ 17<br>R2 [ 18            | 48 ST<br>47 SE                               |                       |

|                                    | R3 🔲 19                       | 46 🗍 K/L                                     |                       |

|                                    | R4 [] 20<br>R5 [] 21          | 45 D L8<br>44 D L4                           |                       |

| 1                                  | B6 🗇 22                       | 43 L2                                        |                       |

|                                    | B7 □ 23                       | 42 L1                                        |                       |

|                                    | R8 [ 24<br>R9 [ 25            | 41 DS2<br>40 DS1                             |                       |

| 1                                  | R10 26                        | 39 🔲 K8                                      |                       |

|                                    | R11 ∐ 27                      | 38                                           |                       |

|                                    | R12 🔲 28<br>R13 🔲 29          | 37 K2<br>36 K1                               |                       |

|                                    | R14 🔲 30                      | 35 🗎 INIT                                    |                       |

|                                    | R15 [] 31                     | 34 VDD<br>33 DIVTEST                         |                       |

|                                    | X4 □ 32                       | DIVIES!                                      |                       |

\*The user determines which R outputs are appropriate for a specified device emulation.

Note the device descriptions.

NC – NO INTERNAL CONNECTION

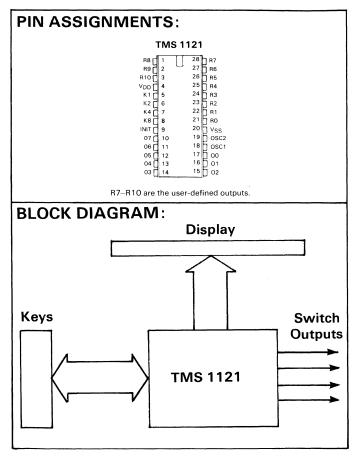

# TMS 1121/1122

### UNIVERSAL TIMER CONTROLLER

### **FEATURES:**

- 4 independent switch outputs.

- 18 daily or weekly times.

- Display of day of week, am/pm, output status, on/off/ sleep status.

- 4 digit display.

- 50 Hz or 60 Hz operation.

Reference Manual: 'TMS 1121/2 Universal Timer Control Manual'.

### **DESCRIPTION:**

Program time-setting and switch selection is entered via the keyboard.

A 4 digit display and 18 individual LED's display system status. Timing is derived from a 50 or 60 Hz mains input, according to a

link-option switch.

TMS 1121 is a 12 hour clock; TMS 1122 is a 24 hour clock.

### **CHARACTERISTICS:**

| Supply voltage         | 9V     |

|------------------------|--------|

| Typical supply current | 5 mA   |

| Max. R output drive    | 28 mA  |

| Temp. range            | 0-70°C |

### **ORDERING INFORMATION:**

Part No. TMS 1121 NLL TMS 1122 NLL

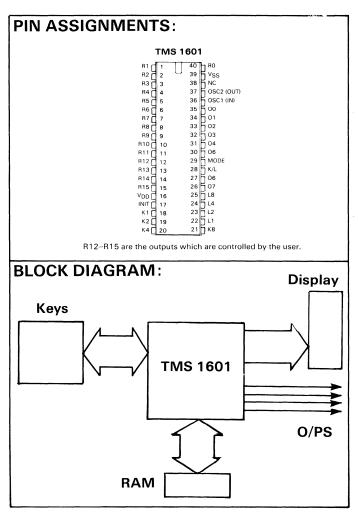

# **TMS 1601 NLL**

### PMOS CONTROLLER/TIMER

### **FEATURES**

- 4 independent switch outputs.

- 28 weekly times.

- 4 daily times.

- 24 hour clock on 4-digit display.

- 7 day sequence, or shorter.

Reference Manual: 'TMS 1601 NL Controller/Timer User Guide'.

### **DESCRIPTION:**

The TMS 1601 is a pre-programmed microcomputer from the TMS 1000 family. It controls 4 outputs according to switch times which are entered via a keyboard and stored in an external RAM memory.

The outputs are controlled by time of day or week and the state of each output, and the system as a whole is displayed using a 4-digit LED display and 19 individual LED's. Timing is derived from a 50 Hz mains input.

### **CHARACTERISTICS:**

| Supply voltage                                         | 9V       |

|--------------------------------------------------------|----------|

| Typical supply current Max. R output drive Temp. range | 11 mA    |

| Max. R output drive                                    | 28 mA    |

| Temp, range                                            | 0–70°C I |

### **ORDERING INFORMATION:**

Part No. TMS 1601 NLL

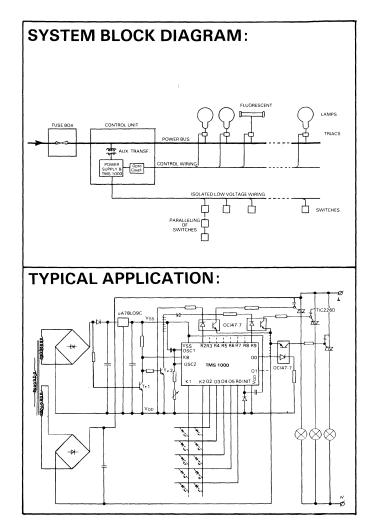

# **TMS 1019**

### MICROPROCESSOR BASED LIGHTING SYSTEM

### **FEATURES:**

- 8 lamps on/off, incandescent or fluorescent.

- 2 dimmer lamps.

- 1 lamp with timed fading.

- 1 lamp for intruder alarm or flash light communication.

- Addition of further TMS 1000 increases number of controlled lamps to 24.

- Low voltage switches (9V, 1 mA isolated) are completely safe and easy to parallel up to same lamp.

- Zero-voltage switching prolongs life of incandescent lamps.

### **DESCRIPTION:**

The TMS 1019 is a pre-programmed microcomputer which controls up to 12 lamps according to push buttons.

Variations in brightness are achieved by adjusting the triac firing angle – there is one triac for each lamp in the system.

All wiring to and from wall switches is low voltage and isolated (mains is supplied only to the ceiling rose) so, compared with conventional lighting systems, cheaper wire is used without sacrificing the safety advantage.

### ORDERING INFORMATION:

Part No. TMS 1019 NLL

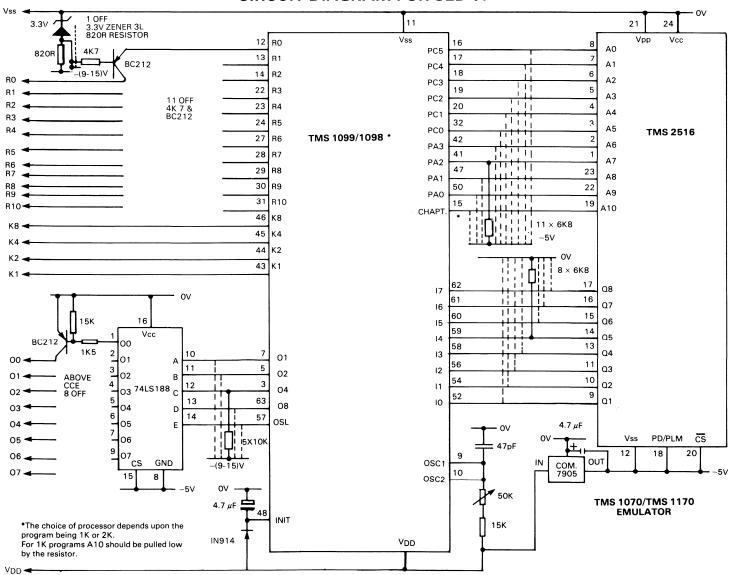

### SYSTEM EMULATION BOARDS

### **FEATURES:**

- True emulation of masked microcomputers.

- Single power supply operation (9V or 15V selected by a link).

- Uses 25XX Eproms.

- Easy to change the value of pulldown resistors.

- Adjustable clock speed.

- Emulates High Voltage (1 × 70) devices without any modifications.

- Dimensions only  $160 \times 100$ mm.

### **DESCRIPTION:**

SEB's are populated PCB's which emulate TMS 1000 microcomputers.

SEB 1 = TMS 1000/1070/1200/1270/1100/1170/ 1300/1370.

SEB 2 = TMS 1400/1470/1600/1670.

SEB 3 = TMS 1000C/1200C/1100C/1300C.

They contain all the components which are fabricated onto the masked microcomputer. The only major difference between SEB's is that the SEB 2 has 2 extra links for setting the ratio for the divider on the K8 input.

All SEB's have a 40 pin double sided edge connector for linking to the prototype board.

### **CIRCUIT DIAGRAM FOR SEB 1:**

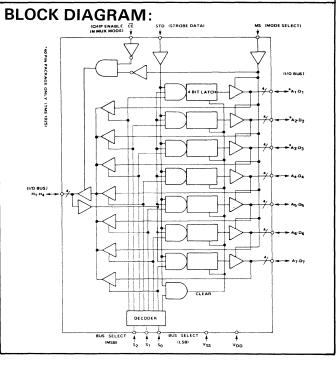

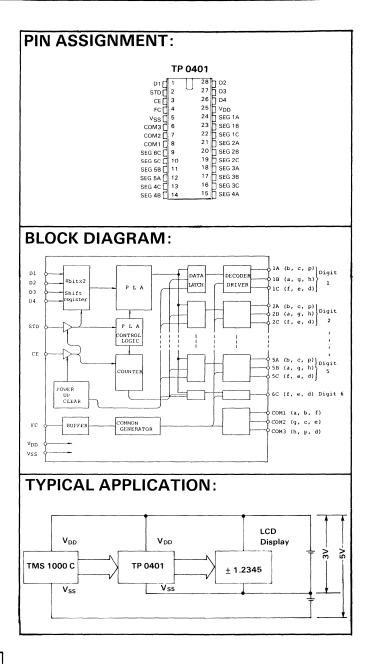

### LIQUID CRYSTAL DISPLAY DRIVER

### **FEATURES:**

- 5<sup>1</sup>/<sub>3</sub> digit, 9 segment direct drive LCD driver.

- Latched outputs.

- CMOS technology.

- 28 pin package.

- Compatible with TMS 1000 family.

### **DESCRIPTION:**

The TP 0401 can directly drive LIQUID CRYSTAL DISPLAYS, under the control of a microprocessor, eg TMS 1000. It uses a chip enable, strobe data, frame clock and 4 data inputs to achieve this operation.

Since it is fabricated in CMOS it's power and voltage requirements are very low. It is available only in CMOS.

### CHARACTERISTICS:

| Supply voltage (typ.)  | 3V     |

|------------------------|--------|

| Supply current (typ.)  |        |

| Frame frequency range1 |        |

| Input current          |        |

| Temp. range            | 0-70°C |

|                        |        |

### **ORDERING INFORMATION:**

Order code: TP 0401

# **APPLICATION TECHNIQUES**

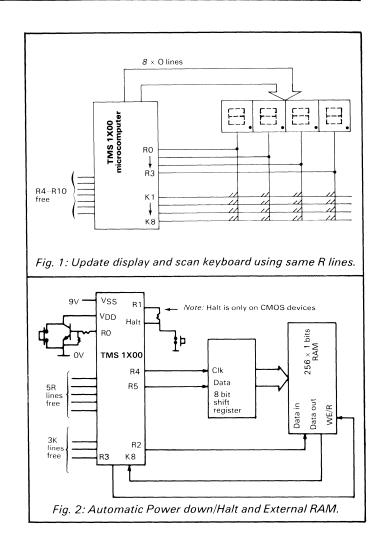

### 1. Display

Can strobe on LED or Vacuum Fluorescent Display of as many digits as the appropriate microcomputer has R lines. Each digit may have 8 segments — usually configured as 7 plus a decimal point.

### 2. Keyboard

Without any external hardware, the biggest keyboard which can be handled is: 4xn, where n is the number of available R lines.

*Note:* If the number of digits in the display is greater than or equal to the number of keyboard columns, then R lines can be made to perform both functions (Fig. 1), otherwise it may be necessary to use O lines to scan the keyboard, in the space between turning off one digit and turning on the next.

### 3. Automatic Power Down and/or Halt

If V<sub>DD</sub> is configured as Fig. 2, then power up is achieved by pushing a button, where upon Rx is set high. In order to power down under program control, Rx is set low.

The "Halt" Mode (CMOS parts only) may be implemented under program control as shown in Fig. 2. When the "restart" button is pressed, program execution continues, and Ry is immediately set low.

### 4. Controlling External RAM

External RAM is often useful for long-term storage of data, especially if CMOS RAM is used.

This can be achieved using only 4 input lines and 1 input line as shown in Fig. 2.

### 5. Use of Link-options

One masked microcomputer can be made to perform a variety of different functions by putting more than one program inside it. The desired function can then be selected by external switches, usually diode links on the PCB.

### 6. A/D Conversion

If A/D conversions are required and a TMS 2100 series microcomputer is not suitable, an external A/D conversion chip (either TL505 or TL507) can be used. Controlling either of these requires only 2 ouput lines and 1 input line.

### 7. Speech Synthesis

Any TMS 1000 microcomputer can control the TMS 5100 speech synthesis chip: I/O requirements are normally 5 output lines and 1 input line.

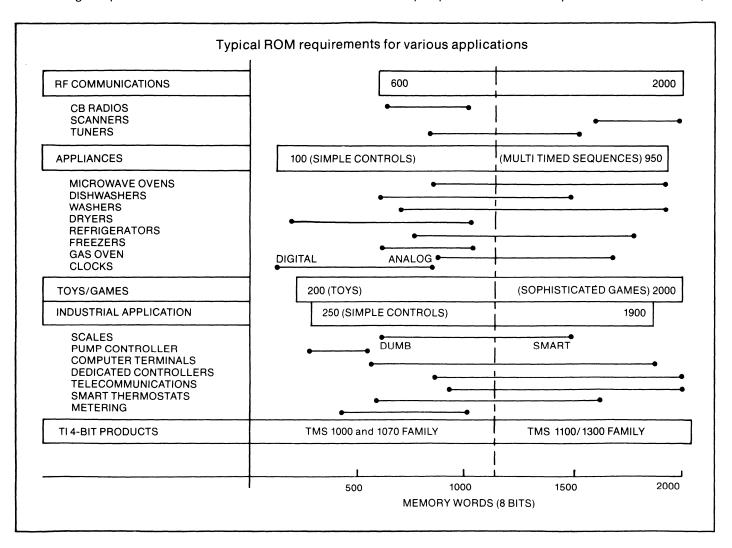

# **Applications**

The users of the TMS 1000 Family are many and varied. Depending upon the speed required, input/output interface, desired power supplies, a wide range of products can be served. To show some

typical examples, the chart below plots application vs. typical read-only-memory (ROM) requirement of those applications to show the wide range and variety of products covered by the TMS 1000 family.

# Applications of TMS 1000 series Microcomputers

### Electro/Mechanical

Accounting Machine

Air Conditioner

Alarm

Annunciator

Appliance Timer

Beverage Dispensing

Coin Changer

Central Clock System

Cash Register

Copy Machine

Door Chimes

Electronic Balance

Fax Equipment

Fuel Metering

Pin Ball Machine

Games

Gas Cooker

Gas Pumps

Juke Box

Photo Processing

Oven Control

Microwave Oven Control

Scales

Temperature Controller

Taxi Meter

Thermometer

Washing Machine

Vending Machine

### Electronic

Automatic Telephone Answering

Automotive Tester

CPU Front Panel

Commercial Building Security

Decibel Meter

Digital Voltmeter

Engine Diagnostic Tester

Evaluator Control

ECR Equipment

Fixed Communication Equipment

Keyboard Encoder

Line Control

M/G Transceiver

Mobile Telephone

Measurement Instrument

Automatic Telephone Recording

Auto Dialer

PBX Equipment

PBX Line Compressor

Pressure Display

Security System

Talking Calculator

Traffic Control

TV Encoder/Decoder

TV Programmer

Numerical Control Display

### **Distributed Computing**

Communication Channel Switch Data Collection Equipment Hand Held Speedometer P.O.S. Terminal Printer Terminal

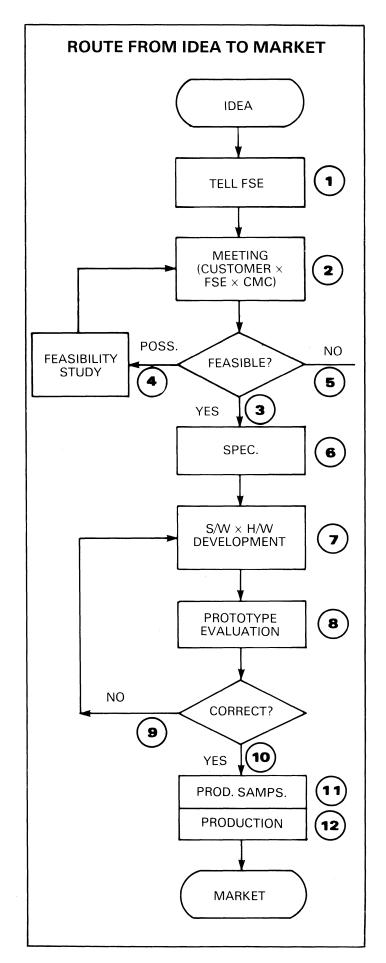

# Masking/Development Timescales

### **Timescales**

- (4) Feasibility studies are usually less than 2 weeks long and can be free of charge.

- (6, 7, 8) This is the time between agreeing a specification and demonstrating a complete prototype. It ranges from approximately 8 weeks for a standard 1K program to 20 weeks for a complex 4K program.

- (11) Once the customer has checked out the program, masked samples can be produced in approximately 12 weeks.

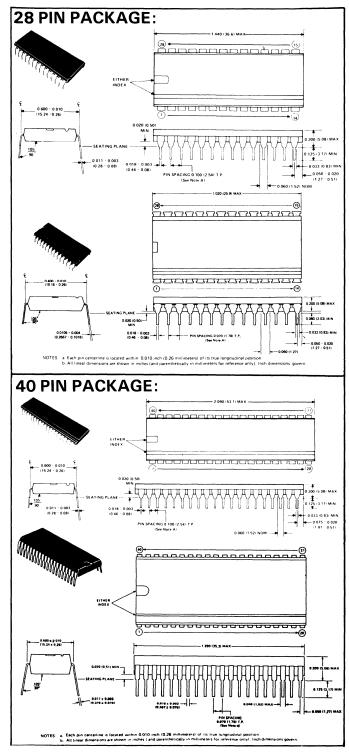

# Packages/Reliability

### **FEATURES:**

- 20 pin 0.3" package with 0.1" spacing.

- 28 pin 0.6" package with 0.1" spacing.

- 28 pin 0.4" package with 0.07" spacing.

- 40 pin 0.6" package with 0.1" spacing.

- 40 pin 0.6" package with 0.07" spacing.

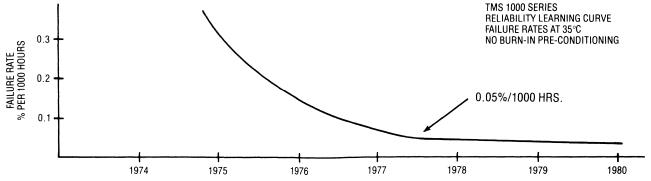

- 0.05%/1000 failure rate.

### **DESCRIPTION:**

Most of the devices in the TMS 1000 family are available in a wide variety of packages.

Shrunk packages (0.07" pin spacing) are very useful in any application where board area is at a premium.

### **High Reliability**

Reliability of TI's PMOS TMS 1000 Series is demonstrated by an attained failure rate of 0.05%/1000 hours now! Six years and millions of devices experience pays off in long system life and minimal service expense. The TMS 1000 reliability, coupled with the reduced package count possible with the TMS 1000 family provides longer life and lower costs for your products.

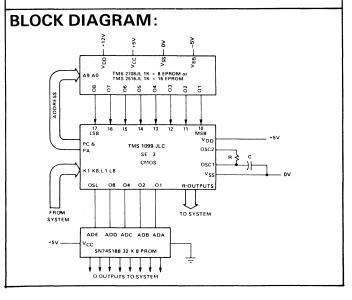

### **FAMILY DESCRIPTION:**

The TMS 7000 family is a range of 8 bit microcomputers containing on-chip CPU, RAM, ROM and I/O. They are not restricted however to accessing internal memory only but can through expansion modes address up to 64K bytes. Each device even contains the ability to disable it's internal ROM and turn into a powerful 8 bit microprocessor!

The instruction set is also the most powerful on any 8 bit microcomputer of a similar price offering unique features and features only found on more expensive devices.

It may be that in some situations even the standard instruction set is not powerful enough and this is where the TMS 7000 family comes into it's own. The family also goes under the name of the MicroLanguage Processor (MLP), which means that the instruction set is micro-programmable and can be defined by the user to suit his own application.

Current devices are produced in NMOS technology but as time progresses a variety of parts will become available. Plans are already being carried out to produce low power NMOS parts and CMOS too. Time will also reveal devices containing other than just the standard features available at present. Such is TI's committment to the 8 bit market.

### **DEVELOPMENT SUPPORT**

No microcomputer is of any use if there are no development tools available to develop programs and emulate the devices. TI has developed a system called MLP Front Panel which will allow on a TI minicomputer the writing, assembling, debugging and emulating of any TMS 7000 program. This system will also allow emulation of custom microcode.

An evaluation module is also available which allows the development of small programs and the emulation of the final program prior to mask development. Larger programs can be developed on a minicomputer using cross-support software and downloaded to the module for debugging and emulation.

TI will also undertake to write TMS 7000 programs to a customer's specification at it's plant in Bedford. Experienced engineers are available to produce a complete system design including the hardware and software.

| A5 A            | 6   | RESET    | - N T 1 |            | N<br>T     | 1              | E-SCALI<br>TIMER<br>CONTROL | 14           | 7 44 | A3 A2    | A    | ·    | _     |                  | A0                    |              |   |    |  |

|-----------------|-----|----------|---------|------------|------------|----------------|-----------------------------|--------------|------|----------|------|------|-------|------------------|-----------------------|--------------|---|----|--|

| н               | 1   |          | Ľ       | γ.         | Ċ          | ┸—             |                             |              |      |          |      | 7    |       |                  | 82                    |              |   |    |  |

| нз              | L   | DEC      | ODE     | BUF        | _          | TIME           |                             | av 8v22      |      | N. B. C. |      |      |       |                  | 81                    |              |   |    |  |

|                 |     |          |         |            | _          | VO CONT        |                             | 2K BYTE      |      |          |      |      |       | 128              | 80                    |              |   |    |  |

| osc             |     | MIC      | RO      |            |            | NTRY P         | OINT                        |              |      |          |      |      |       |                  |                       |              |   |    |  |

| <b></b>         | 1   |          |         |            |            | IR             |                             |              | USER |          |      | Ž    |       | BYTE             | 87                    |              |   |    |  |

| H2              |     |          |         |            |            | <u> </u>       |                             | STATUS       |      |          |      |      |       | ROM Y- DECODING  | BIT ROM/RAM COMMON 10 | 32 SENSE AMP |   | B5 |  |

| H4              | ١.  | CO       | DE      |            | -          | BCD<br>SHIFTER |                             | PROGRAMMABLE |      |          | 3    | 3    | Ì     | V <sub>2</sub> - |                       |              |   |    |  |

| <b></b>         | L   |          |         | BUFFER     |            | ALU            |                             |              |      | Š        | O SE | 32.8 |       | CHG P            |                       |              |   |    |  |

| D7              |     | 1        |         | 1          | -          | MD - P/N       |                             |              |      | 4        |      |      |       | 86               |                       |              |   |    |  |

| D6              |     | 1        |         | MCX &      |            | Ť              |                             | MASK ROM     |      | •        |      | -    | RAM   | $\vdash$         |                       |              |   |    |  |

|                 |     | RC       | М       |            | _          | PCH<br>PCL     |                             |              |      |          |      | 1    |       |                  | 84                    |              |   |    |  |

| D5              |     |          |         | 174T20     |            | SP             |                             |              |      |          | П    |      |       |                  |                       |              | П |    |  |

| D4 MAL          |     |          | MAL     |            |            |                |                             |              |      |          |      |      |       | <b>B</b> 3       |                       |              |   |    |  |

| D4              |     | <u> </u> |         | ¥          | l          | AI<br>BU       | DOR<br>FFER                 | <u> </u>     |      |          | L    | L    | L     |                  | RAM                   |              |   |    |  |

| D3              |     | ME       | WOR     | <u>.</u> . | L          |                | X-DEC                       |              |      | Y-BUFF   |      | FF   | X-DEC | MC               |                       |              |   |    |  |

| D CONTR         | OL. | _        | HIMC    | n. 4       | GRP DECODE |                |                             |              |      |          |      |      |       | IIIC.            |                       |              |   |    |  |

| D2              |     | ∐,       | я       | D          | ,          | co             | C1                          | C2           | СЗ   | C4       |      | C    | 5     | C6               | C7                    |              |   |    |  |

| V <sub>cc</sub> |     |          |         |            |            |                | <u> </u>                    |              |      | <u> </u> |      |      |       | <u> </u>         |                       |              |   |    |  |

The TMS 7020 bar layout using Tl's new Strip Chip Architecture Topology (SCAT).

### PRODUCTION OF DEVICES

Once a program has been finalised TI will take the source or object file of the program and use it to generate masks from which the first sample devices are produced. This process takes 16 weeks. Assuming the samples are found satisfactory then full production devices can be available 16 weeks later: TI will normally consider production on any device over 5K units in quantity.

# TMS 7000 Family

### STANDARD INSTRUCTION SET

### **PROGRAMMING THE TMS 7000**

The TMS 7000 family has taken the advantages of memory to memory and register to register architectures and combined them to achieve a powerful combination of speed and flexibility. The programmer is not restricted to operating on data only in an accumulator nor does he have to consume valuable bytes of program specifying frequently used registers.

This has been achieved by including within the opcodes of certain instructions an implication to one of two registers out of the 128 available. This has the effect to treating them more as accumulators than registers, yet still retaining them within the memory map. It also saves one byte of code since the register is implied. These two registers are known as the A and B registers.

All of the common addressing modes encountered in memory to memory architecture have been included. These are direct, indirect, indexed, program counter relative, and immediate addressing. In addition to these are register A, register B, register file and peripheral file addressing giving a total of nine addressing modes.

Since the RAM, ROM, I/O and external addresses are all within the memory map there is no need to include special instructions to reference these areas. The extended addressing modes specify an unqualified 16 bit address and may access any area within the 64K address range.

Programming is made still easier by the inclusion of the dual operand instructions. One operand being known as the source, the other as the destination. Most microcomputers when using these common instructions (i.e. add, subtract, AND, move etc.) require at least one of the operands to be a CPU register (like A or B) but with the TMS 7000 family any RAM location can be the source and any RAM location can be the destination.

### **SINGLE OPERAND INSTRUCTIONS:**

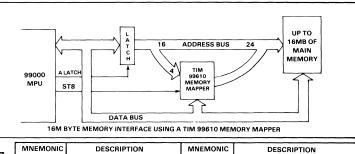

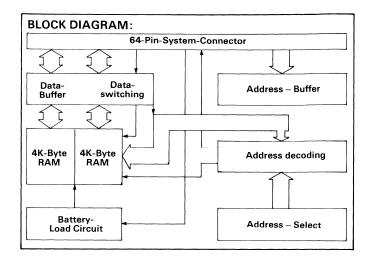

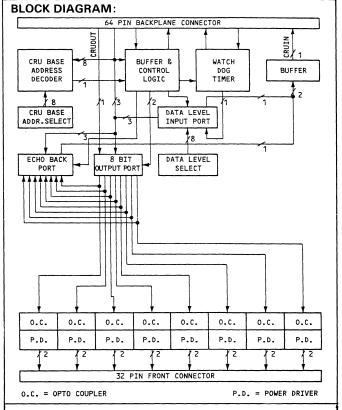

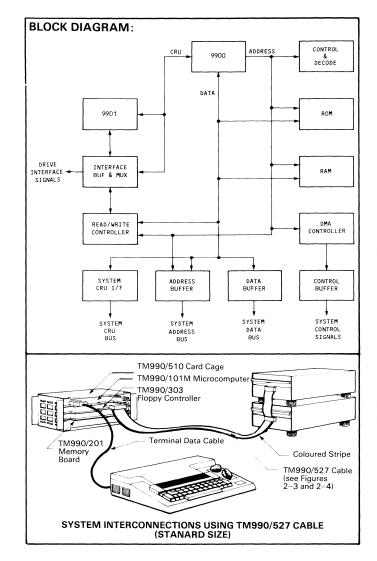

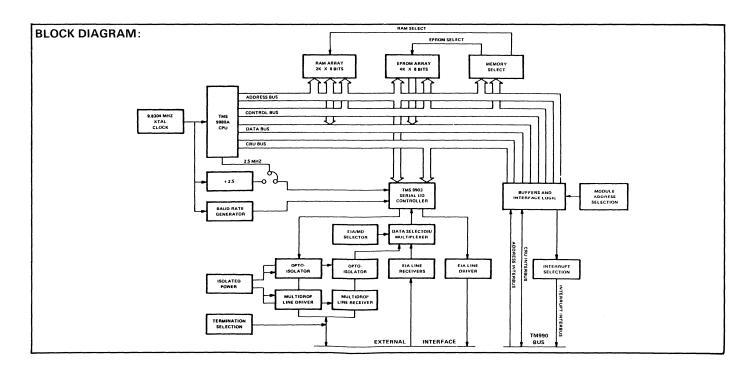

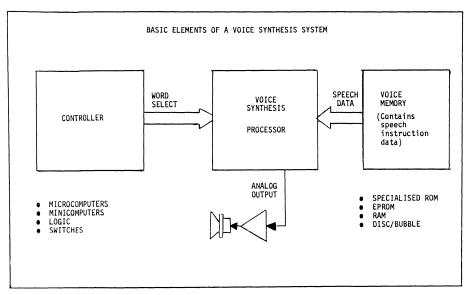

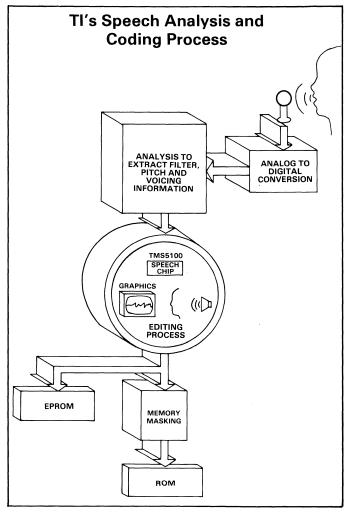

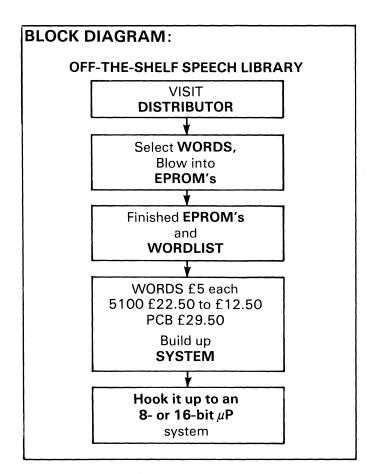

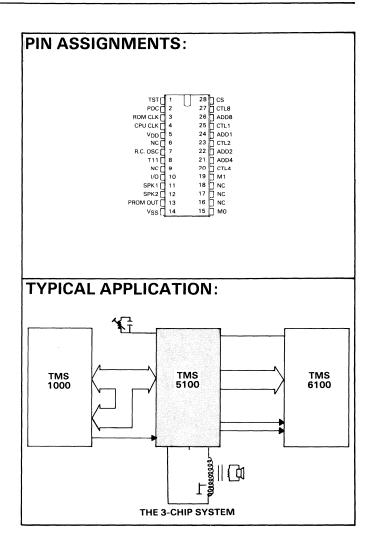

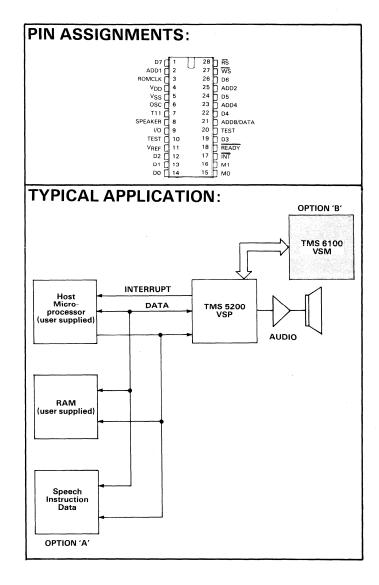

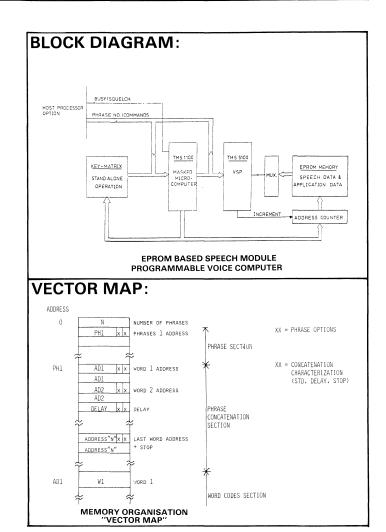

| MNEMONIC                                         | MEANING                                                                                                                                                                                                  |